# COMPUTER ORGANIZATION UNIT-1

SIR C R REDDY COLLEGE OF DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING ENGINEERING

Dr DEEPAK NEDUNURI

ELURU.

ASR-10-1.1

# Computer Organization (co)

#### UNIT-I

Syllabus: Basic structure of Computers:

JNTUK RIG 2-2-CSE

- Functional Units

- Transfer of the second

- Basic Operational concepts

- Bus stouctures

- Sylvem Software

- Performance

- The history of computer development

#### TEXT-GOOK :

1. Computer Organization, Carl Hamacher, Zvonks Vranesic, Safea Zaty, 5th Edition, McGraw. Hill

# 1 Computer types:

- omputer is a fast electronic calculating machine that accepts digitized input information, processes it according to a list of internally stored instructions and produces the resulting output information.

- -> The list of instructions is called a <u>Computer program</u>, and the Enternal storage is called <u>computer memory</u>.

- -> The different computer types are,

- is Desktop computers

- personal computer

- (i) notebook Computers

- (iii) Work Stations

- (IV) Enterprise Systems

- (V) Servey

- (vi) Super Computers.

Type text pp Computers have processing and storage units, visual diplay and DDADEBRAK output units, and a keyboard that can all be located easily on a

home 100 office desir

-> The mest storage media includes,

- havd disks

- CD-ROMS etc.

-> The most common form of destatop computers is personal computer, which has found wide use in homes, schools, and business officer.

-> Postable notebook Computers are a Compact version of the personal Computers with all of those Components packaged into a single unit the size of a thin briefcase.

-> Westestations have more computational power than personal computers, used in engineering applications, especially for interactive design work.

-> Enterprise Systems (or) Mainfrances, are used for business data processing in medium to large corporations that require much more computing Power and storage capacity than workstations can provide.

-> Servers contain sizable database storage units and are capable of handling large volumes of requests to acress the data.

-> Super compuler none used for the large-scale numerical calculations required in applications such as weather frecastly and aircraft design and Simulation.

# 2) Functional Units.

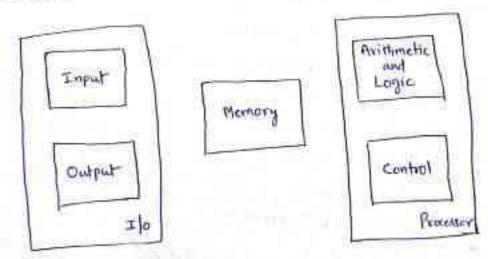

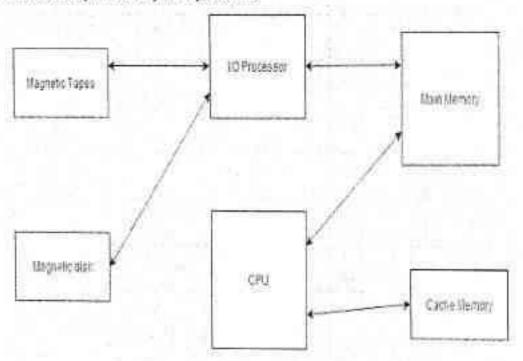

-> Basic Functional Units of a Computer is depicted as,

[Type text] DDr DEEPAK

- -> A computer consists of five functionally independent main parts

- -input

- memory

- Arithmetic and Logic

- output and

- control unit.

- -> Instructions (or) Machine Instructions, are explicit commands that

- govern the transfer of information within a computer as well as between the computer and its I/o devices.

- specify the axittenetic and logic operations to be performed.

### (i) Input Unit .

- -> computers accept coded information through input units, which read the

- -> The most west-known input device is the Keybrand.

- -> The other Input devices are,

- Mouse

- Joyahok

- SCANNATI

- Touch Screen

- Light Pen, .. etc-

# (ii) Memory Unit.

- -> The function of the memory unit is to store programs and data.

- -> There are two classes of storage

- -Primary

- Secondary

- -> Primary Storage is a fast memory that operates at electronic speeds.

- -> Programs must be stored in the memory while they are being executed.

- -> The Psimary memory of a Computer in RAM (Random Access Memory)

- Programs have to be stored, particularly for information that is accessed infrequently

- -> The different Secondary Storage devices are

- HOD (Hard disk drive)

- FDD (floppy date drive)

- Magnetic disks and tags

- optical disks (CD-ROM) - compact disk Read Only Hong

B/s

[Type text] DDr DEEPAK

# (11) Arithmetic and Logic Unit:

- -> Most computer operations are executed in the arithmetic and Logic unit

- -> Consider an example, Suppose two numbers located in the memory are to be added.

- -> They are brought into the processor, and the actual addition is coveried out by the ALU.

- -> The lum may then be stored in the memory (ur) retained in the processor

# in Output Unit;

- -> The output unit is the counter part of the input unit.

- -> Its function is to send processed results to the outside world.

- -> The different output devices are

- Mouitor

- Printer

- Plotter

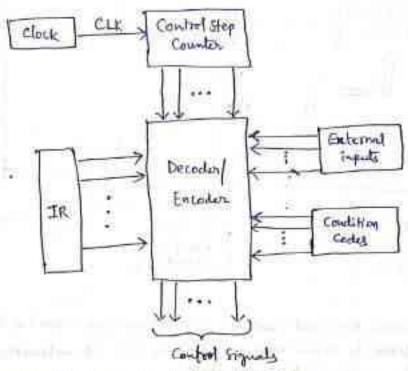

#### My Control Unit:

- -> All activities inside the machine are directed and controlled by the

- -> The contest unit is effectively the nerve center that sends control signals to other units and senses their states.

# 3 Basic Operational Concepts

- Transfers between the memory and the processor are started by sending the address of the memory breation to be accessed to the memory whit and issuing the appropriate control signals.

- -> The data are then francferred to con from the memory.

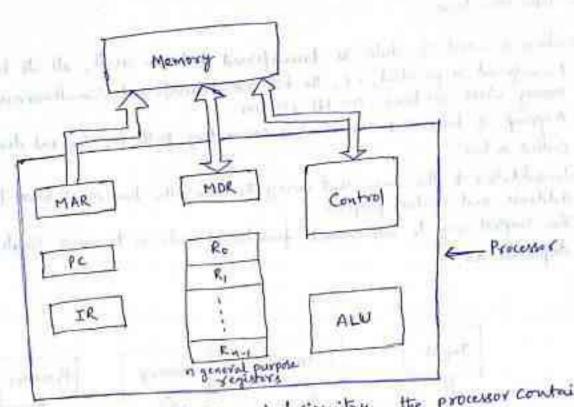

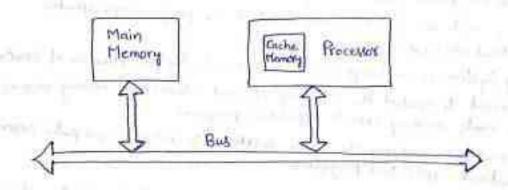

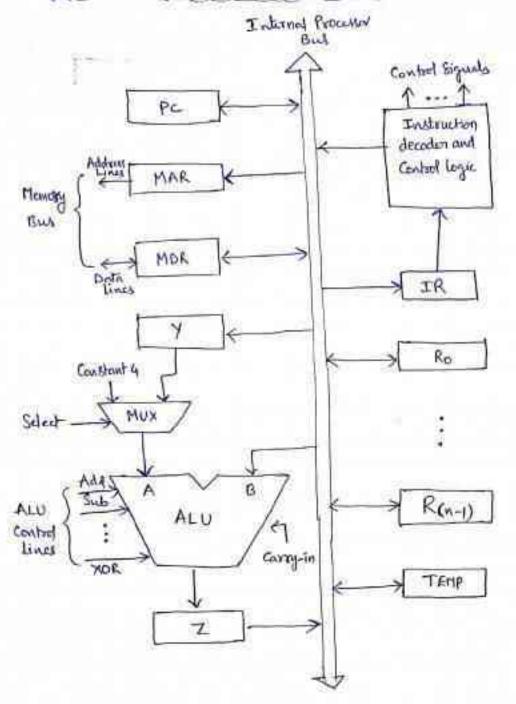

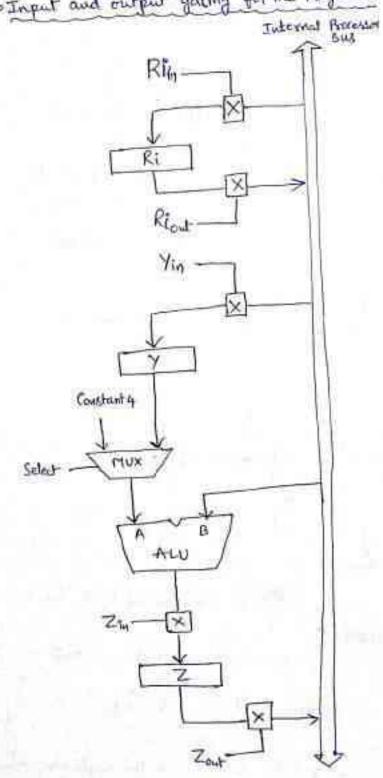

-> The connections between the precessor and the memory is depicted

11-30/4

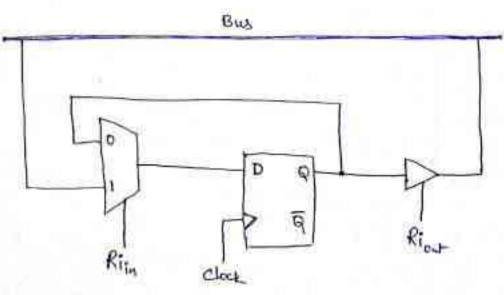

- -> In addition to the ALU and the control circuitry, the processor contains a number of negisters used for several different purposes.

- -> The Instruction Register (IR) holds the instruction that is enverently being

- -> Its output is available to the control circuit, which generates the timing signals that constrol the various processing elements involved

- -> The Program Counter (PC) keeps track of the execution of a program and it contains the memory address of the next instruction to be fetched and

- -> During the execution of an instruction, the contents of the PC are updated to correspond to the address of the next instruction to be executed.

- -> The PC points to the mext instruction that is to be fetched from memory.

- -> It has also n-general purpose registers to through Rn-1

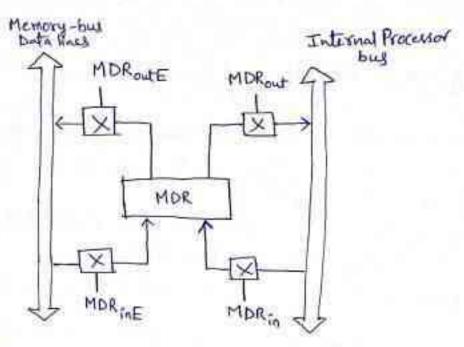

- -> Finally, two registers facilitate communication with the memory

- -> These are the Memory Address Register (MAR) and

all produced the sold the describery

# Memory Data Register (MDR)

-) The MAK holds the address of the location to be accessed.

Type text OR contains the date to be written into (ox) read out of the addressed DDr DEERAK

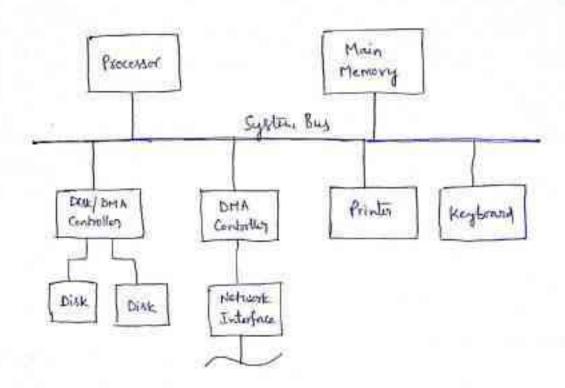

# (4) Bus Structures;

- when a word of data is transferred between units, all its bits wie transferred in parallel, i.e, the bite are transferred simultaneously over many wires, or lines, the lit per line .

-> A group of lines that soives as a connecting path for several devices is

Called a but.

-> In addition to the lines that carry the data, the bus must have lines for address and control purposes.

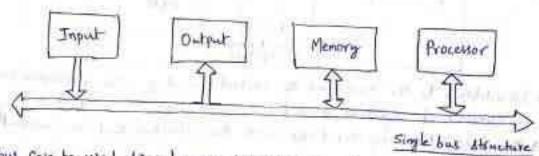

-> The simplest way to interconnect functional units is to use a single bus is depicted as,

-> The bus can be used for only one transfer at a time, only two units can actively use the bus at any given time.

-> Bus control lines are used to axbitvate multiple requests for use of the

-> The main virtue of the single-bus structure is its loss cost and its flexibility for attaching peripheral devices.

-> Systems that contain multiple bases achtere more concurrency in operations by allowing two (or) more transfers to be consided out at the same time

-> This leads to better performance but at an increased cost.

# (5) Software: (System software)

-> In order for a user to enter and run an application program, the computer must already contain some system software in its memory.

-> System software is a collection of programs that are executed as needed to perform functions such as,

- Receiving and Interpreting user commands.

- Entering and Editing application programs and Morning them as files in secondary storage devices.

- Managing the Storage and retrieval of files in secondary storage [Type text] DDr DEEPAK

- Running standard application programs such as processors, spreadsheets, (01) games, with data supplied by the user.

- Controlling I/o units to necessar input information and produce output results.

- Translating programs from source form prepared by the user Tota object form consisting of machine instructions.

- Linking and running uson-written application programs with existing standard library routines, such as numerical computation protages.

- -> System Software is thus responsible for the Coordination of all activities in a Computing System.

- -> Application Programs are usually written in a high-level programming language, such as C, C++, Java, in which the programmer specifies mathematical (3) text-processing operations :

- -> Operating System is a large program, (or) actually a collection of routines, that is used to control the shaving of and interaction among various computer units as they execute application programs.

- -> The OS routines perform the tasks required to assign computer hesources to individual application programs.

- -> A system program that all programmers use is a text editor. It is used for entering and editing application programs.

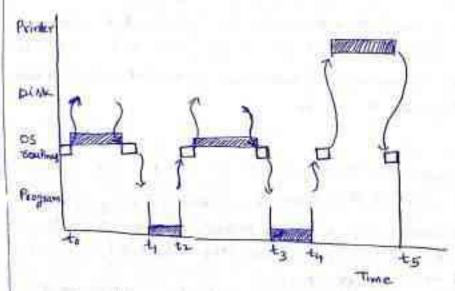

- -> User Program and OS routine showing of the processor is depicted as

DPP DEFPAKS called as multiprogramming (20) multitasking

# 6) Periformance

-> The most impostant measure of the performance of a computer is

how quickly it can execute programs.

-> The speed with which a computer executes programs is affected by the design of its hardware and its machine language instructions.

-> To represent the performance of the processor, we should consider only the periods during which the processor is active.

-> These are the periods labeled program and as routines. The sum of these periods as the processor time needed to execute the program.

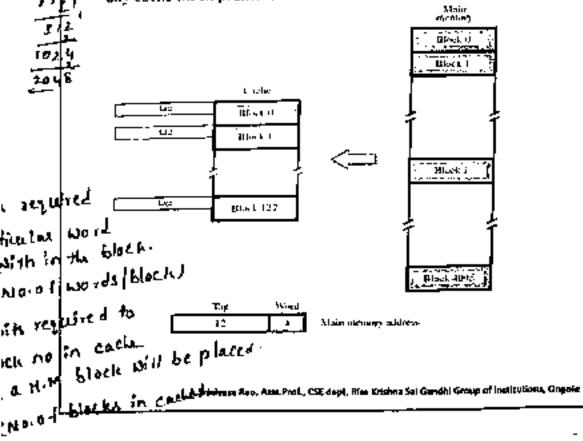

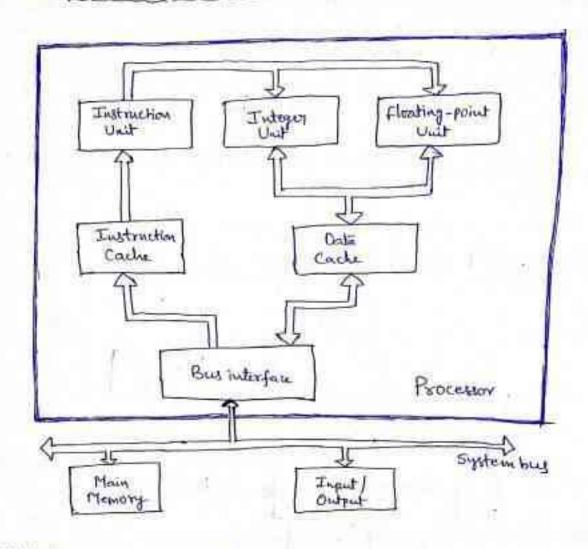

The processor cache is depicted as

-> At the start of execution, all program instructions and the prequired duta are stoled in the main memory

- As execution proceeds, instructions and fetched one by one over the bus that the processor, and a copy is placed in the cache

-> When the execution of an instruction calls for data located in the main memory, the data one fetched and a copy is placed in the cache

-> Later, if the same instruction for data stem is needed a second-time, it is read directly from the cache.

# (1) Procemor clock;

-> Processor circuits are controlled by a timing signal called a clock

-> The clock defines regular time intervals, called clock cycles

-> To execute a machine instruction, the processor divides the action to be performed into a sequence of basic steps, such that each step can be completed in one clock cycle.

-> The length P of one clock cycle is an impostant parameter that [Type text] processor performance

**DDr DEEPAK**

- -> Its inverse is the clock Rate, R= 1/P, which is measured in cycles per second.

- -> In standard electrical engineering terminology, the term cycles per second is called Hertz

# (1) Basic Reformance Equation:

-> Let T be the provenor time graquited to execute a program

-> Assume that complete execution of the program rusquires the execution

of N machine language instructions.

-> The number N is the actual number of instruction executions, and is not necessarily equal to the number of machine instructions in the object Program.

-> Suppose that the average number of basic steps meeded to execute one machine instruction is S, where each basic step is completed in one clock cycle.

-) It the clock mate is R cycles per second, the program execution time

it given by

$T = \frac{N \times S}{R}$

This is greferred at Basic Performance Equation

# (iii) Pifelining and SuperScalar Operation;

-> A substantial improvement in performance can be achieved by overlapping the execution of successive instructions, using a technique called pipelining.

#### -> Consider the instruction

#### Add RI, Rz, R3

- which adds the contents of registers RI and Rz, and places The sum late R3.

- The contents of RI and RZ are four transferred to the inpute of the

- After the add operation is performed, The sum is transferred to R3.

- The processor can read the next instruction from the memory while the addition operation is being performed.

[Type text] Then if that instruction also uses the ALU, its operands can be DDr DEEPAkranifered to the ALU inputs at the sametime that the result of the Add instruction is being transferred to R3.

-> A higher degree of concurrency can be achieved if multiple instruction pipelines are implemented in the processor.

-> This means that multiple functional units are used, creating parallel paths through which different instructions can be executed

in parallel.

-> with such an arrangement, it becomes possible to start the execution of several instructions in every clock cycle. This mode of operation is called Superscalar execution.

#### (10) Clock Rate .

- There are two possibilities for increasing the clock rate, R.

- first, improving the Integrated Circuit (Ic) technology makes logic counts faster, which reduces the time needed to complete a basic step

This allows the clock period, P, to be reduced and the clock

- Second, reducing the amount of processing done in one basic step also makes it possible to ruduce the clock period P.

# (V) cise and Rise.

- Simple instructions nequire a small number of balls steps to execute

- -> complex instructions involve a large number of steps.

- -> A key consideration in comparing the two choices is the use of pipelining.

- -> CISC and RISC are used for complex instructions.

- -> CISC Complex Instruction Set Computers

RISC Reduced Instruction Set Computers.

#### (vi) Compilers.

- -> A compiler translates a high-level language program into a sequence of machine instructions.

- -> To reduce N, we need to have a suitable machine instruction set and a compiler that makes good use of it.

- -> An optimizing compiler takes advantage of various features of the target processor to reduce the product NXS, which is the total number DEEPARlock cycles needed to execute a program.

# (Vii) Performance Measurement;

- -> Computer designars use performance estimates to evaluate the effectivency of new features.

- -> Manufacturers use performance indicators in the marketing process.

- -> Buyers use such data to choose among many available computer models.

- -> The computer community adopted the idea of measuring computer performance using benchmark programs.

- -s To make comparisons possible, standardized programs must be used.

- -> The performance measure is the time it takes a computer to execute a given benchwark.

- -> The accepted practice today is to use an agreed-upon selection of neal application programs to evaluate performance.

- -> A remprefit Organization called SPEC (System Performance Evaluation Corporation) selects and published representative application programs for different application domains, together with test results for many Commercially available computers.

- > The SPEC rating is computed as,

Running time on the reference computer

Running time on the computer under test.

- -> The overall SPEC taking for the computer is given by

where is it the number of programs in the suite.

# (7) The History of Computer Development:

- -> Computers as we know them today have been developed over the past 60 years

- -> A long stow evolution of mechanical calculating devices proceded the development of computers

- -> Davelopment of the technologies used to fabricate the processors, memories, and Ilo Units of computers has been divided into four generation.

- ti) First Generation (1945-55)

- (1) Second Generation (1955-65)

[Type text] DDr DEEPAK (11) Third generation (1965-75)

(iv) Fourth Generation (1975 - Present)

# With First Generation.

- -> The Key concept of a Atored program was introduced by John von Neumann

- -> Programs and their data were located in the same memory, as they are - LUCIAY .

- Assembly language was used to prepare programs and was translated not machine language for execution.

- -> Basic arithmetic operations were performed in a few milliseconds using vacuum tube technology to implement logic functions.

- -> Magnetic core memories and magnetic tape storage devices were also developed.

# (11) The Second Generation:

- -> The transistor was invented at AT&T Bell Laboratories in the late 1940s and quickly replaced the vaccoum tube.

- This basic technology shift marked the start of the second generation

- -> Magnetic core memories and magnetic drum storage devices were more widely used in the second generation.

- -> High-level languages such as FORTRAN were developed.

- -> Compilers were developed to translate these high-level language programs into a corresponding assembly lauguage program.

- -> Separate I/O Processors were developed

- -> IBM became a major computer manufacturer during this time.

# (iii) The Third Generation:

- -> The ability to fabricate many transistors on a single silicon chip, called Integrated Circuit (Ic) technology developed.

- -> Integrated circuit memories began to replace magnetic cole memories.

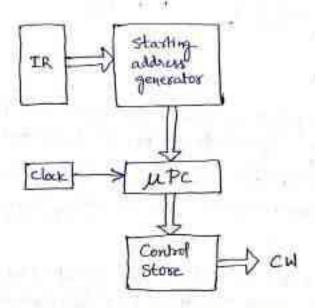

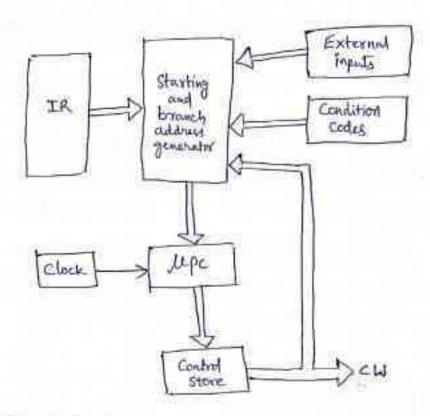

- -> Other developments included the introduction of microprogramming, parallelism, and Pipelining

- -> Openating System roftware allowed efficient sharing of a Computer system by several wer programs.

- -> Cache and vixtual memories were developed.

- -> Cache memery makes the main memory appears faster than it neally is, and vistual memory makes it appear larger.

- -> System 360 mainframe computors from IBM and the line of PDP minicomputers from Digital Equipment Corporation were dominant commercial [Type text] of the third generation. **DDr DEEPAK**

# (iv) The Fourth Generation.

-> Tend of thousands of transistors could be placed on a single chip, and the name Very Lange Scale Integration (VLSI) was coined to describe this technology.

-> VLSI technology allowed a complete processor to be tabuscated on a

single chip called Hicroprocessor.

-> Companies such as Intel, National Semiconductor, Motorola, Texas Instruments, and Advanced Hicro devices, were the driving forces of this technology.

-> Organizational concepts such as concurrency, pipelining, caches, and virtual memories evolved to produce the high-performance computing

systems of today is the

-> Portable Notebook Computers, desktop PCs, and Workstations, interconnected by local area networks (LAN), WAN (Wide area networks), and the Internet.

-> Centralized Computing on mainframes is now used primarily for business

applications in large Companies.

# COMPUTER ORGANIZATION UNIT-2

# SIR C R REDDY COLLEGE OF ENGINEERING DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

Dr DEEPAK NEDUNURI

ELURU.

# Computer Organization UNIT-2

ASR-C0-2-1

THTUK RIL 2-1 CSE

Syllabus: Machine Instruction and Programs

- Instructions and Instruction Sequencing

- Register Transfer Notation

- Ascembly language Notation

- Ballic Instruction-types

- Addressing Medes

- Basic Input Output Operations

- The Role of Stocks and Queus in Computer Programming Equation

- Component of Instructions

- Logic Instructions

- Shift and Retate Instructions.

#### Text Book

- 1. Computer Organization, Carl Hamacher, Zvonks Vranesic, Safea Zaky, 5th Edition, McGraw Hill

- 1 Instructions and Instruction Sequencing:

- -> A computer must have instructions capable of performing four types of operations.

- Data transfers between the memory and the processor registers.

- Antimetic and Logic operations on data

- Program sequencing and control.

- Ilo Transfery,

- (i) Register Transfer Notation,

- -> We need to describe the transfer of information from one location in the computer to another.

- -> Possible locations that may be involved in such transfers are membly locations, processor registers, (or) registers in the Ilo subsystem.

- -> Name for the addressed of memory locations may be LOC, PLACE, A, VARZ processor register names may be Ro, R5 and I/O They will names may be DATAIN, OUTSTATUS, and so on.

The contents of a location are denoted by placing square brackets around the name of the location.

Example: RI & [LDC]

- means that the contents of memory location Loc one transferred into processor register R1.

Example: R3 + [R1] + [R2]

- means the operation that adds the Contents of registers R1 and R2 and then places their sum into register R3.

- -> This type of notation is known as Register Transfer Notation (RTM)

- -> The right-hand Side of RTN is always devotes a value and the left-hand side is the name of a location where the value is to be placed.

# (1) Assembly Language Notation,

-> Assembly language Format is a notation to represent machine instructions and programs.

Example; Move Loc, RI

- Here data transferred from memory location LOC to processor register RI

- The contents of Loc wie wet unchanged by the execution of this instruction, but the old contents of Register R1 one overwhiten.

# Example: Add RI, RI, RS

- Here, adding two numbers contained in processor registers RI and RL and placing their sum in Rs can be specified by the assembly language statement

Add RE

# (iii) Basic Instruction Types:

-> There are 4 types of Instructions available

- a) Three address Instructions

- b) Two address Instructions

- c) One-address Instructions

- d) testi-address Instructions

# a) Three-address Instructions:

-> An instruction having three openands

Syntax Opcode Sources, Sources, Destination

Example Adding two numbers

- where A,B are called Source operands, c is called destination operand. - opcode means operation cake.

#### b) Two-address Instructions

-> An instruction having two openands

Syntax: opcode Source, Destination

Example: Move B,C (: C < [B])

ADD A,C (: C < [A] + [C])

### c) One-address Instructions

-> An instruction having only one operand

. True Parlington

a processor register, called Accumulated is used.

# d) Fero-address Instructions:

-s An instruction having zero openands.

-> It was stack operations push and pop to perform operations.

```

(: TOS ( (A))

PUSH A

Example:

(: TOS ( [B])

PUSH B

(: TOS ← (A]+[B])

A DD

POP C ("C ← (TOS))

Another Example: EvaluateX=(A+B) +(C+D)

ADD A,B, RI (" RI E (A] + [B])

Three Address:

ADD C, D, R2 ( : R2 + [c] + [D])

MUL RI, RE, X ( : X + [RI] + [RI])

Two Address:

MOU A, RI (- RI + (A))

ADD B, RI (: RI + (B))

MOV C, R2 ( : R2 ← [c])

ADD D, RL ( ! RL + [R] + D)

MUL RI, RZ (" RZ & [R] * [R])

Mov Rey * (" x < [RL])

One-Address:

LOAD A (" AC C [A])

ADD B ( AC = [AC]+[B])

STORF TI (: TI ( [AC])

LOAD C ( ACE[C])

ADD 0 (" AC ( AC) +(D))

MUL T1 ("AC ←(A) + [TI])

8

STORE X (" X = [Ac])

PUSH A ( TOS - [A])

PUSH B (: TOS ← [B])

([DI+[A] > 20T:) GOA

PUSH C (: TOS < [C])

```

0

Zero - Address PUSH D ("TOS ~ [D]) (': Tos ←[6]+[0]) ADD MUL ("(10) + ((1) + ((1)) + ((1))) ( :: x ← [ to ] ) Pop x

# (2) Addressing Modes:

- -> The different ways in which the location of an operand is specified in an instruction are referred to as Addressing Modes.

- -> The different Generic Addressing Hedes is given as

| S- No | Name                      | Assembler Syntax | Addressing function      |

|-------|---------------------------|------------------|--------------------------|

| 1     | Immediale                 | # value          | Operand = Value          |

| 2     | Register                  | R;               | EA = RI                  |

| 3     | Absolute (Direct)         | Loc              | EA = LOC                 |

| н     | Indihect                  | (R1)<br>(Loc)    | EN = [LOC]               |

| 5     | Index                     | × (R1)           | EA = [RI] + X            |

| G     | Base with Index           | (R;,R;)          | EA = [R:] + [R]]         |

| 7     | Base with index and offer | × (Ri, Ri)       | EA = [Ri] + [Rj] + X     |

| 8     | Relative                  | ×(Pc)            | EA = (CC) + X            |

| 9     | AutoIncrement             | (Ri) +           | EA = [R:]; Increment R;  |

| to.   | Auto Decrement            | - (Ri)           | Document Ri<br>EA = [Ri] |

# (1) Implementation of variables and constants:

- -> In Assembly language, a variable is negresented by allocating a register (or) a memory location to hold its value.

- -> There are two addressing modes to access variables a) Register mode b) Absolute mode.

#### \*) Register Mode:

-> The openand is the contents of a processor Registers Example : Move RI, R2

Here RI, PL are registery.

# +) Abartute (Direct) Hode:

- The openand is in a manify territory Example ADD A/6

-> Address and Data constants are represented in Agreembly language living the Immediate mode.

# 1) Immediate Mede;

-> The operand is given explicitely in the instruction.

Example: MOVE #200, Ro

- places the value 200 in Register Ro

→ # high indicates that this value is to be used as an immediate operand.

#### Example :

MOVE B, RI ADD #7, RI MOVE RI, A

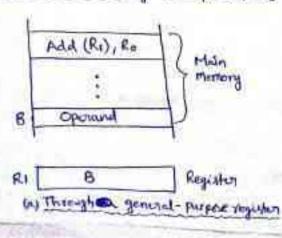

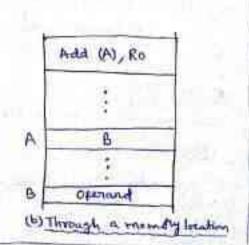

# (ii) Indirection and pointous;

-> In Addressing modes, the instruction does not give the operand (01) its address explicitly.

-> Instead, it provides information from which the memory address of the operand can be determined. This address is called as Effective Address(EA)

#### \*) Indirect Mode,

-> The effective address of the openand is the contents of a register (or) memby location whose address appears in the instruction

-> we dende indirection by placing the name of the register (e) the memory address given in the instruction in parantheses.

-> Indirect Addressing is depicted as

- (A) To execute the Add instruction, the processor used the value of B, which is register RI, as the effective address of the openand.

- It requests a read operation from the memory to read the contents of levation 6.

- The value read is the desired opened, which the processor adds to the Contents of register Ro.

- (b) In Indirect Addressing through a memory location, the processor first Treads the Contents of momeny location A, then requests a second read operation using the value B as an address to obtain the operand. - The register (on memory frontion that contains the address of an operand

- is culted a pointer. -> Consider the C-language statement

A = + 6;

- where B is a pointer variable This Atracement may be compiled into

MOVE BIRI MOVE (RI) A

- Using imhorest addressing through memory, MOVE (B), A

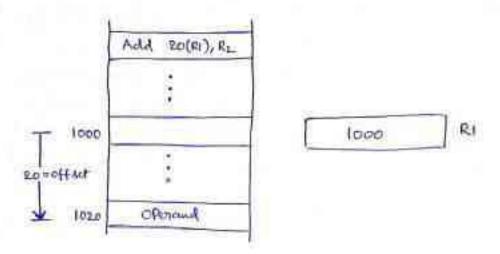

# (iii) Indexing and Arrays;

- It is well in dealing with lists and Arrays

# \*) Index Hode:

- The effective address of the openand is generated by adding a constant value to the contents of a negister

- The register used may be either a special register (21) general-purpose regelter Called Index register.

- Index mode Symbolically nepresented as,

X (8:)

where X denotes the constant value contained in the instruction RI denotes the name of the register involved. - The effective address of the operand is given by

EA = X+[Ri]

- -> The contents of the index register are not changed in the process of generating the effective address

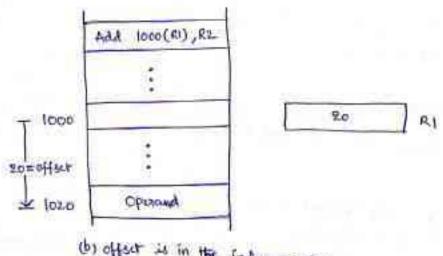

- -> Two ways of using Index mode (Index Addressing) is depicted as,

#### (A) Offset is given as a constant

-> The index segretar RI contains the address of a memory location, and the value X defines an offset (cor) displacement) from this address to the location Where the openand is found.

(b) offset is in the Index register

- -> Here, the constant X corresponds to a memory address, and the contents of the tindex register define the offset to the openand.

- -> In either case, the effective address is the sum of two values - one is given explicitly in the instruction, and - Its other is stored in a regular.

# (14) Relative Addressing:

- -> Index mode is used for general-purpose processor registers

- -> In Relative Addressing, the program counter (PC) is used instead of a general purpose register.

#### \* Relative Hode:

- -) The effective address is determined by the Index mode using the program counter in place of general purpose register &:

- -> Relative mode Symbolically represented as,

X(PC)

- The effective address of the operand is given by

- -> This morte can be used to access data operands

# (v) Additional Modes:

- (9) Autoincrement Hoche

- (h)-Antodecrement Mode

#### \* Autoincrement Hode;

- -> The effective address of the openand is the contents of a register specified in

- -> After According the operand, the contents of this register are automatically incremented to point to the next item in the list.

- -> Symbolically represented as

- It normally increments one, but in byte-sized operands (or) byte-addressable memory

1 for 8-bit operands 2 for 16-bit operands 4 for 32-bit operands.

- The effective Address of the openand in

# (\*) Autodecrement Hode:

- -> The contents of a negister specified in the instruction are first automatically decremented and are then used as the effective address of the openand

- Symbolically represented as,

-> The effective address of the openand is

# (3) Basic Input/Output Operations:

- -> Ito operations are essential, and the way they are performed can have a significant effect on the performance of the computer.

- -> Contrider a task that neads in character input from a keyboard and produces character output on a display screen. A simple way of performing Such Ifo tasks is to use a method known as program - controlled Ifo

- The mate of datatransfer from the keyboard to a computer is limited by the typing speed of the user, which is unlikely to exceed a few chamitery persecond

- -> The trate of output transfers from the computer is determined by the grate at which characters can be transmitted over the link between the computer and the display device, typically several thousand characters py second.

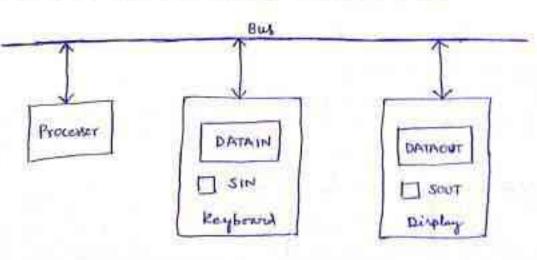

- -> Bus connection for processor, keyboard, and display are deficted as

- -> The Keyboard and the display are sporate devices.

- -> Consider the problem of moving a character code from the keyboard to the

- -> Striking a key stores the corresponding character code in an 8-hit buffer register associated with the Keybrard.

- -> Let us call this register DATAIN

- -> To inform the processes that a valid character is in DATAIN, a status could that I SIN, is set to 1.

- -> A program monitors SIN, and when SIN is set to 1, the processor reads

- -> When the character is transferred to the processor, SIN is automatically cleared to 0.

- -> It the second character is entered at the keyboard, SIN is again set to I and the process repeats.

- -> When characters are transferred from the processor to the display, a buffer register, DATABUT, and the status Countrel Hay, SOUT, are used for this transfer.

- -> The buffer registers DATAIN and DATAOUT and the Robater flags SIN and SOUT are part of circuity commandy known as a device Interface.

#### Example:

-> The processor can monitor the keyboard status flag SIN and transfer a character from DATAIN to Register RI by the following sequence of operations

READWAIT Branch to READWAIT IF SIN = 0

Input from DATAIN to RI

-> Sequence of operations used for transferring output to the display is given as,

WRITEWAIT Branch to WRITEWAIT If SOUT = 0

OUTput from RI to DATAGUT

-> The contents of the Keybonord character buffer DATAIN can be transferred to Register RI in the processor by the instruction

MOVEBYTE DATAIN, RI

-> Similarly the contents of Register RI can be transferred to DATAOUT by

MOVEBYTE RI, DATAGUT

# 1 The Role of STACKS and QUEVES in Computer programming Equation

- -> Insider to organize the central and information linkage between the main program and the subsoutine, a datastructure called a stack is used.

- -> A stack is a list of data elements, words for bytes, with the accessing mentriction that elements can be added (or) removed at one end of the list only.

- -> It uses a pointer variable called Top of the Stack.

Example: - pile of Trays in a cafeteria

- Customen pickupnew trays from the top of the pile, and clean trays are added to the pile by placing them onto the top of the file.

- -> Stack uses LIFO (Last In First Out) mechanism, which describes the last data item placed on the stack is the first one hemoved when restricted begins

- -> PUSH and POP are the operations of stack, which describes placing the new item on the stack and removing the top item from the stack, respectfully

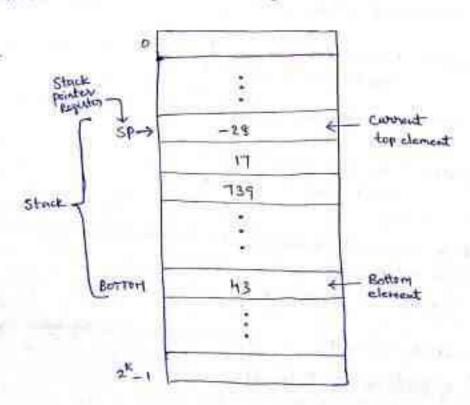

- -> Data Atored in the memory of a computer can be organized as a stack, with successive elements occupying successive memory locations.

- -> A stack of words in the memory is depicted as

- -> It contains numerical values, with 41 at the bottom and -28 at the top.

- -> A processor register is used to keep track of the address of the element of the stack that is at the top at any given time, could stack pointer (SP)

- -> In a byte-addressable memory with a 32-bit word leagth, the PUSH operation can be implemented as,

50B #4, SP MOVE NEWLITEM, (SP)

-> The pop operation can be implemented as

MOVE (SP), ITEM #4, SP

-> If the processor has the Autoincrement and Autodecrement addressing modes, then the push operation can be performed by the single instruction

MOVE NEWITEH, -(SP)

-> The pop operation can be performed by the zingle instruction

HOVE (SP) + , HEWITEH

- -> Another useful datast suctions that is similar to the stack is called Queue

- -> Data are stored in and retrieved from a queue on a Float in first out (FIFO) bosts.

- -> Here, new data we added at the back (high-address end) and retrieved from the point (low-address end) of the quene.

- -> It uses too pointery FRONT and REAR.

- -> INSERT and DELETE are the operations of queue.

# (5) Components of Instructions:

- (i) Logic Instructions

- (1) Shift and Rotate Instructions

# ii) Logic Instructions;

-> Logical operations such as AND, OR, and NOT, applied to Individual bits, are the basic building blocks of digital circuits

-) It is also useful to be able to perform logic operations in reflevate

Example: I's complement

NOT DST

- Complements all bits contained in the destination operand, changing o's to 1's and 1's to 0's

Example: 214 Complement

NOT RO

ADD #1, RD

-> Many computers have a single instruction for 2's complement NEGATE RO

-> Logical operators AND, OR, NOT represented as bits in a table as,

| l,  | ۵ | ė  | r | Ĺ | ٢  | ۴ | ١ |

|-----|---|----|---|---|----|---|---|

| - 1 | - | ۲, | ۰ | 7 | ٠. | ъ | A |

| Operadi | openondo | AND |

|---------|----------|-----|

| 0       | 0        | 0   |

| .0      | T)       | 10  |

| 1c      | 0        | 0   |

| T.      | (1)      | 13  |

#### OF

| operands | Openaud2 | OR |   |

|----------|----------|----|---|

| 0        | 0        | 0  |   |

| 0        | a 1      | t  | l |

| î .      | 0        | 4  |   |

| t        | А.       | 1  |   |

#### NOT

| орелана | Not |

|---------|-----|

| 0       | N/  |

| , i     | 0   |

# (ii) Shift and Rotate Instructions.

- (a) Shift Instructions

- -> There are many applications that require the bits of an operand to be Ahisted right for) left some specified number of bit positions.

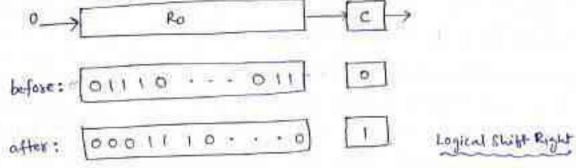

- -> There are 2 types of Shift Instructions des Legical Shift Instructions

- (#) Arithmetic Shift Instructions

- (\*) Logical Shift Instructions:

- -> There are 2 logical shift Instructions

- . Logical shift Left (LShiftL)

- · Logical slift Right (LShifter)

- -> These instructions shift an openand over a number of bit positions specified in a count operand contained in the instruction.

- . Logical Shift Left (LShiftL):

- -> The general form of Logical Shift Left Instruction is

[LSWITT Count, DST ]

-> The fount operand may be an immediate operand (or) it may be contained in a processor regist in a processin register.

LShitt #1, Ro

-> This is depicted as,

Logical Shift Left

-) It shifts the contents of Register Ro left by two positions -> Vacated positions are filled with 014.

| Shift Rigi | M-,                                                       |

|------------|-----------------------------------------------------------|

| wind form  | in,                                                       |

| LShiftR    | Count, DST                                                |

|            |                                                           |

|            |                                                           |

| \          | Ro                                                        |

|            | Shift Right  What -form  [LShift R  LShift R  depicted as |

- -> It shifts the contents of register Ro right by two bit paritions.

- vacated peritons one filled with zerox.

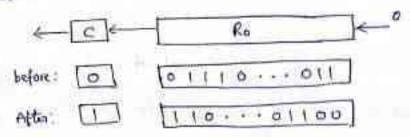

# (4) Arithmetic Shift Instructions:

- -> There are two types in Arithmetic Shift instructions

- · Arithmetic Shift Left (-Askift L)

- · Arithmetic Shift Right (Archifte)

# · Arithmetic Shift Left:

Ashith #2, Ro

- -> A Left Asistametic shift of a binary number by 2 positions

- -> The empty positions in the LSB (Least Significant Bit) are filled with

Arithmetic Shift Left

- -> It works same like Logical Shift Left operation

- · Arithmetic Shift Right

Ashifter #2, Ro

- A right arithmetic shift of a binary number by 2 pointions.

- -> The empty positions in the MSB (Most Significant Bit) are filled with copies of the original MSB bit.

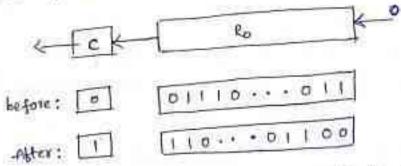

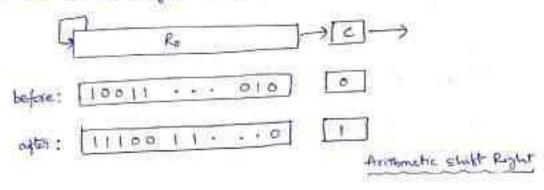

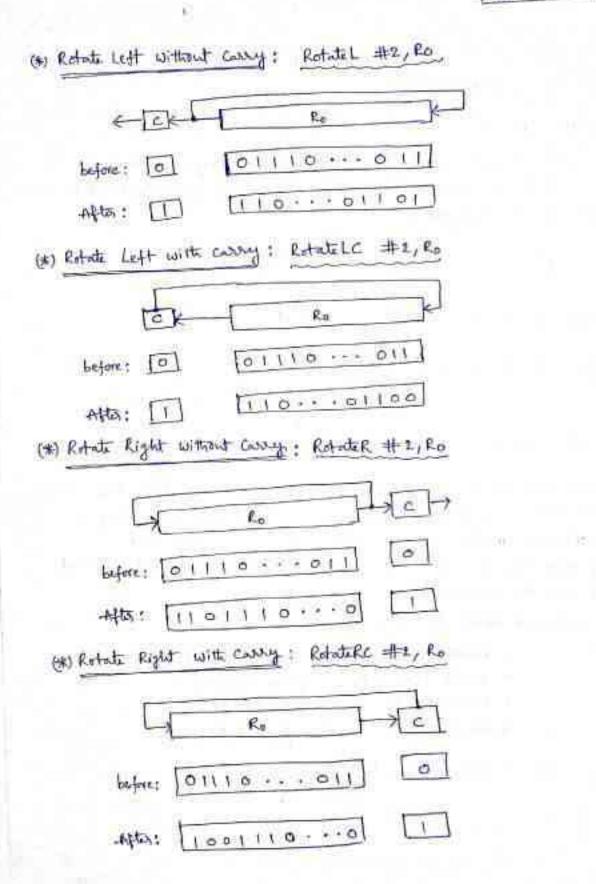

# (b) Rotate Instructions:

- -> In the shift operations, the bits shifted out of the operand one lost, except for the last bit shifted out which is retained in the carry flag c.

- -> To preserve all lists, a Let of rotate instructions can be used.

- -> They move the bits that are shifted out of one end of the openand back into the other end

- -> The different Rotate Instructions are,

- \* Rotate Left without Covery (Rotatel)

- \* Rotate Left with carry (RotateLC)

- \* Retate Right without carry (Retater)

- or Robate Right with carry (RobateRc

- -> The different Rotate Operations are depicted as

# DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING. SIR C R REDDY COLLEGE OF ENGINEERING PT DEEPAK NEDUNURI

ELURU.

#### ASR-ca-3.1

# UNIT-3 : Types of Instructions

# Syllabus .

- Arithmetic and Logic Instructions

- Branch Instructions

- Input Output operations

- Addressing Hodes

# Text Book

1 Computer Organization, Carl Hamacher, Zvonks Vranesic, Safea Zaky, 5th Edition, McGrawttell-

# 1 Arithmetic and Logic Instructions:

- (1) Arithmetic Instructions

- (ii) Logic Instructions

# (1) Arithmeth Instructions.

- + ADD

- 4 SUE

- \* MUL

- FMLA

#### (+) POD:

- The basic Assembly Lewynoge expression for withmetic instruction is

# Opcode Rd, Rn, Rm

- where the operation specified by the Oficale is performed using the operands in general-purpose sujulins Rn and Rm.

- The result is placed in Registers Rd

- Instead of being contained in Register Rm, the Second Openand can be given in the immediate mode

-> The second operand can be shifted (or) rotated before being being used in the operation.

JNTUK CSE 2-2 RIL

-> when a shift (or) rotation is neguined, the instruction is given as

- Here, the second operand, which is contained in Register R5, is shifted left 4 bit peritions, and it is then added to the contents of Register R1

- the sum is placed in Register Ro

MATRIAG

( SUB :

# (\*) MUL!

- -> Two versions of a Multiply instruction core provided.

- (1) The first version multiplies the contents of two registers and places the low-order 32-bits of the product in a third register. The high-order bits of the product, if there are any, are discorded. Example:

added to the product before storing the vesselt in the destination

- This is called Hultiply - Accumulate Operation

- It is used in numerical algorithms to digital signal processing.

#### (li) Logic Instructions:

-> The different Logic Instructions are,

\* AND

+ OL

\* xor (exclusive or)

\* BIK (Bit-Clear)

-> Logic Instructions have the name format as the Arithmetic Instructions

- which is a bitular logical AND between the operands in Registers Rn and Rm

#### Example :

- If register Ro Contains the hexadecimal pullers 02 FA 62 CA and RI Contains the pullers 0000 FFFF, then the result 0000 62 CA being placed in segister Ro.

## Examples:

-> The BIC (Bit-clean) instruction is closely related to the AND instruction

-> It complements each bit in openand Rm before Andring them with the bits in register Rn

-It Ro is 02FA6ICA and Ro is 0000FFFF, then the result is 01FA0000 being placed in Ro.

-> The MOVE NEGATION instruction, with the OP-code mnerabale MVNI, Complements the bits of the source openand and places the result in Rel

Example: MUN RO, R3

-SIF the contents of R3 are the hexadecimal puttern ofofofof, then it places the result fofofofo in register Ro

# (2) Branch Instructions.

-> Conditional branch instructions contain a signed, 21s complement, 24-bit offset that is added to the updated contents of the program counter(PC) to generate the branch transet address

### Marchandrok designar

-> The format for the branch instructions is depicted as,

| 31 18     | 27 24 23 |        | 0 |

|-----------|----------|--------|---|

| Condition | OPcode   | Offset |   |

Instruction Format

atermination of a Branch Target Instruction

- -> The BEQ (Branch if Equal to 0) causes a branch if the Z flag is set to 1

- -> The condition to be tested to determine whether (of) not branching should take place is expecified in the high-order 4-bits, b\_31-28, of the instruction word.

- -> A Branch instruction is executed in the same way as any other ARM instruction, that is, it is executed only if the current state of the Condition code flags corresponds to the condition specified by the condition field of the instruction

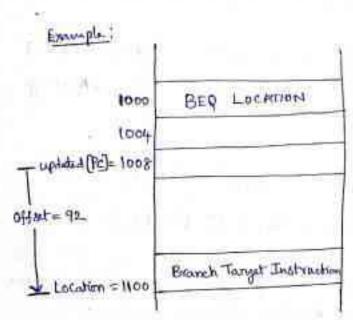

- -> In Example, If the Branch instruction is at address Location 1000, and the branch target address is 1100, then the offset has to be 92 because

the contents of the updated PC will be 1000+8 = 1008 when the address 1100 is Computed.

# (i) Setting Condition Codes:

- Some instructions, such as COMPARE, given by

CMP Ra, Ray

- which performs the operation,

[Rn] - [Rm]

- have the sale purpose of setting the condition code flags based on the result of the subtract execution.

-> On the Other lived, the continuetic and Loyal instructions affect the condition and flags only if explicately specified to do so by a bit in the CP code field.

-> This is indicated by expressing the suffex S to the assembly language Op-rode ninemonic

Example:

- The Instruction

ADDS ROIRI, RZ

sets the condition code flags, but

ADD Ro, Ro, FL

does not

# (3) I O Operations:

-> The ARM architecture uses memory-mapped I/O

-> Reading a character from a keyboard (or) bending a character to a display can be done using program - controlled I/o

-> Suppose that bit 3 in each of the device status registers INSTATUS (Keyboroud) and OUTSTATUS (display) contains the Yespective control flags SIN and SOUT

-> Also assume that the keyboard DATAIN and display DATAOUT registers are located at addresses INSTATUS +4 and DUTSTATUS+4 immediately following the status register locations.

-) The great and write want loops can then be implemented as, Example:

- Assume that address INSTATUS has been located in to Register RI

- The instruction sequence given as,

| READWAIT | LDR  | $R_3$ , $[R_1]$ |

|----------|------|-----------------|

|          | TST  | R3,#8           |

|          | BEQ  | READWAIT        |

|          | LDRB | R3, [R1,#4]     |

- It reads a character into register R3 when a key has been prussed on the keyboard

- The test (TST) instruction performs the bitwise logical AND operation on its two operands and sets the condition Code flags based on the result

- The immediate operand 8 has a single one in the bit 3 position.

- -Thoufore the susult of the TST operation will be zero if bit 3 of Instatus is Zero and will be nonzero if bit 3 is one, signifying that a character is available in DATAIN .

- The BER instruction branches back to READWAIT if the freshle 11 tero, looping until a key u pressed, which sets bit 3 OF INSTATUS to Die.

- Assuming that address OUTSTATUS has been loaded into register R2.

The instruction sequence is given as,

WRITEWAIT LDR R4, [R2]

TST R4, #8

BEQ WRITEWAIT

STRB R3, [R2,#4]

- It sends the character in Register R3 to the DATAOUT register When the display is neady to necesive it.

# (1) Addressing Modes:

-> The 68000 processor addressing modes is depicted in a table as,

| Name              | Assembler Syntax                 | Addressing Hodes           |  |

|-------------------|----------------------------------|----------------------------|--|

| Immediate         | # value                          | Operand = Value            |  |

| Abadute Short     | Value                            | EA = Sign Extended Invalue |  |

| Absolute Long     | Value                            | EA = Value                 |  |

| Register          | Rn                               | EA = Rn (Operand = ERn)    |  |

| Register Indicact | (An)                             | EA = [An]                  |  |

| Indexed basic     | Walue (An)                       | EA = WValue + [An]         |  |

| Indexed Full      | BValue (An, Rk.5)                | EA = BValue + [An] + [RE]  |  |

| Relative basic    | WValue (Pc) (er) Label           | EA = WValue + [PC]         |  |

| Relative Full     | BValue (PC, RK.S) er) Label (RK) | EA = BValue + [PC] + [RK]  |  |

| Auto increment    | (An) +                           | EA = [An] Increment An;    |  |

| Autodecrement     | - (An)                           | Decrement An EA = [An];    |  |

<sup>-&</sup>gt; The 68000 processor have several addressing modes.

#### (1) Immediate Mode:

- The operand is contained in the instruction

- Fowt sizes of openands can be executived, Byte, Word, Long-word, OP-code word.

- The fourth size consists of very small numbers that can be

included directly in the OP-code word of some instructions. (ii) Absolute Mode: (Direct Mode)

- The absolute address of an operand is given in the instruction, following the OP code.

- Those are two versions of this mode long and short.

- In the long made, a E4-bit address is specified explicitly.

- In the short mode, a 16-bit value is given in the instruction to be used as the low-order 16-bits of an address.

- -The sign bit of this value is extended to provide the high-order eight bits of the address.

- Since the sign bit is either O (er) 1, it follows that in the short morte only two pages of the addressable space can be accessed.

- These nove the 0 page and the FFS page, each containing 32K bytes -

## (in) Register Hode:

- The operand is in a processor regular specified in the instruction.

#### (ii) Register Indirect mode.

- The effective address of the operand is in an address suggister specified in the instruction.

#### (M) Bouic Index Hode,

- A 16-bit signed object and an address register, An, are specified in the instruction

- The sum of these offset and the contents of Am is the affective address. of the open and.

# (Vi) Full Index Hode;

- An 8-bit signed offset, an address pregister Am, and an Index register RK (either an address (or) a data register) are given in the instruction.

- The effective address of the openand is the sum of the offset and the contents of negistors Am and Rx

- Either all 32-bits or) the Lign-extended low-order 16 bits of Rx one wed in the derivation of the address.

141 July 2 per 1964

#### (VII) Basic Relative Hode:

-> This is same as the basic Index mode except that the program Counter is used instead of an address geography, Am.

#### (vili) Full Relative Hode;

-> This is some as the full index made except that the program Counter is used instead of an address sugister, An.

#### (ix) Autoincrement stode:

- The effective address of the operand is in an address negister, An, specified in the instruction

- After the openand is accessed, the contents of An are incremented by 1,2,600 4, depending on whether a byte, a word, 600 a Long-word operand, respectively, is involved.

#### (x) Autodocrement Mode:

- The contents of an address register, An, Specified in the instruction are decremented by 1,2,6004, depending on whether a byte, a word, (or) a long-word operand, respectively, is involved.

- The effective address of the operand is the decremented contents of An.

to want or willing out a top of

And the state of the state of

As he has been been an expense over the large

CAR ADDRESS OF THE CONTRACT OF THE PARTY NAMED IN COLUMN TWO AND THE PARTY

The state of the s

# SIR C R REDDY COLLEGE OF ENGINEERING DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

Dr DEEPAK NEDUNURI

ELURU.

# Computer Organization (CO) UNIT-4 I/O Organization

# Syllabus;

- Accessing I/o devices

- Interrupts

- Intersupt Handware

- Enabling and Disabling Interrupts

- Handling Multiple devices. V

- Direct Memory Access /

- Buses

- Synchronous Bus

- Asynchronous Bus /

- Interface Circuits /

- Standard I/o Interface /

- Pexipheral Component Interconnect (PCI) Bus

- Universal Serial Bus (USB)

# 1) Accessing I/o devices:

- -> The basic feature of a computer is its ability to exchange data with

- -> The but enables all the devices connected to it to exchange information.

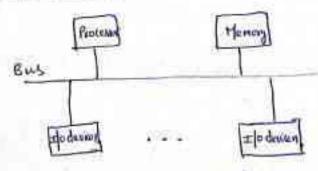

- -> A Single bus Atructure is depicted as

-> Book The bus consists of 3 sets of lines

- Address lines

- Outa lives

- control lines

- Each Ib device is assigned a unique bet of addresses

- when Ito device and the memory short the same address space, the arrangement is called Hemory mapped Ilo.

#### Memory-mapped Ilo:

- with Hemory-mapped Ilo, any machine instruction that can access memory can be used to transfer data to (1) from an Ito device.

#### Example:

MOVE DATAIN, RO (Input Device to Processor Register)

THOSE RO, DATAGOST (Processor Register to Output Device)

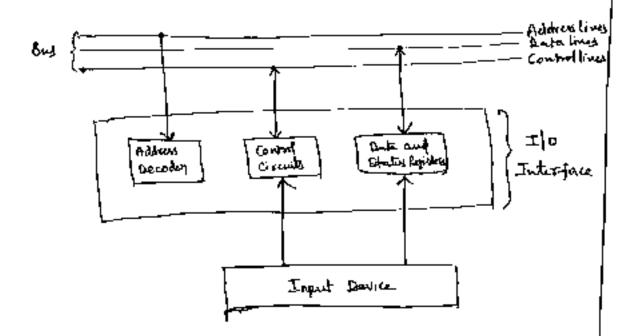

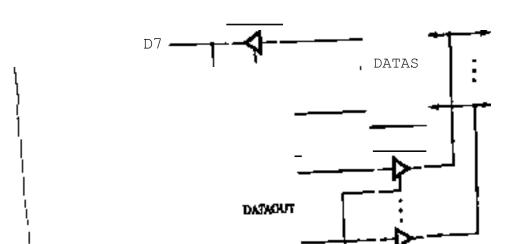

- The I/O Interface for an Input device is depicted as

- How, the address decoder enables the device to recognize its address when this address appears on the address lines.

- .. The data segister holds the data being transferred to (or) from the processor

- The Status register contains information televant to the operation of the Tip device.

(

# @ Interrupts:

- -> An Interrupt stop the continuous progress of an activity by process.

- -> An Interrupt is a signal to the processor emitted by hardware (or) software Indicating an event that needs immediate attention.

- -> the interruption of the current code the processor is executing

- -> The bus control line, called interrupt-request line is used for interrupts.

# i) Interrupt Hardware:

- -> An Ilo device sequests an interrupt by activating a bus line called interrupt-request.

- -> rost computers ours likely to have soveral Ito devices that can request

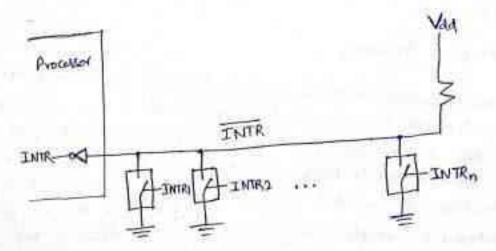

- -> A single intersupt request line may be used to serve n-devices

- -> An equivalent circuit for an open-drain bus used to implement a common interrupt-request line is depicted as

- -> All devices are connected to the line via switches to ground.

- -> To request an interrupt, a device closer its associated switch.

- -> Thus, if all interrupt request signals INTRy to INTRy are inactive i.e., if all switches core open, the voltage on the interrupt-traguest line will be equal to Vag.

- -> This is the inactive state of the line.

- -> Since the closing of one (or) more switches will cause the line voltage to drop to 0, the value of INTR is the logical OR of the requests

from individual devices, i.e,

INTR = INTR + INTR2 + ... + INTRn

- -> The INTR signal is active when in the low voltage state.

- 11) Enabling and Dirabling Intersupts.

- The sequence of events involved in handling interrupt neglicit from a single device are,

- The device sources an interrupt request.

- The processor retessupts the program currently being executed.

- Interrupts are disabled by changing the control bits in the PS (Processor Status register)

- The device is informed that its nequest has been recognized, and in response, it deactivates the interrupt request right

- The action transpersed by the interrupt is performed by the

- Interrupts are enabled and execution of the interrupt program is remained.

# (iii) Handling Multiple devices:

- -> Consider the situation where a number of devices capt capable of initiating interrupts are connected to the processor.

- -> Because these devices are operationally independent, there is no obtained order in which they will generate interrupts.

- -> This situation is handled by 3 methods.

- (9) Vectored Interrupts

- (b) Interrupt Nesting

- (c) Simultaneous Requests

# a) vectored Interrupts;

- -> A device newwasting our interrupt may identify directly to the

- Then the processor can immediately strest executing the corresponding intersupt-service routine.

- -> This laterrupt handling Scheme is known as Vectored Interrupts.

- -> A commonly used scheme is to allorate permanently an over in the memory to hold the addresses of interrupt-service routines.

- -> These addresses are referred as Interrupt vectors, and they are said to constitute the interrupt vector table.

- -> For example, 128 bytes may be allocated to hold a table of 32 interrupt vectors.

## b) Interrupt Nesting:

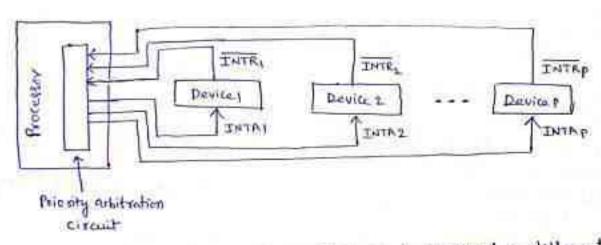

-> Implementation of Julerrupt priority using individual interrupt gagnest and Acknowledge has is depicted as

- -> Here, Each of the futerrupt nequest lines is assigned a different priority level.

- -> Interrupt requests received over these lines are bent to a priority arbitration circuit in the processor.

- -> A neguest is accepted only if it has a higher priority level than that currently assigned to the processor.

#### c) Simultaneous Requests:

- -> Consider the problem of simultaneous arrivals of interrupt requests from two (or) more devices.

- -> The processor must have some means of deciding which trequest to service first.

- -> The processor simply accepts the request having the highest priority.

- -> Priority is determined by the order in which the devices are polled, i.e, the polling the status registers of the I/o devices.

ASR-60-4-6

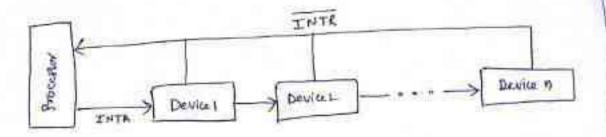

# -> A Daily chain priority interrupt Scheme is depicted as,

- -> The Interrupt request line INTR is common to all devices.

- -> The Interempt-Acknowledge line INTA, is connected in a daisy-chain fashion.

- -> The INTA Signal propagates serially through the devices.

- -> when several devices raise an interrupt request and the INTR line is activated, the processor responds by setting the INTA line to 1.

- -> This xigned is received by devices.

- -> Devices passes the signal on to device 2 only if it does not require any service.

- -> In doing-chain arrangement, the device that is electronically along to the processor has the highest principle.

- -> The second device along the chain has becoud highest priority,

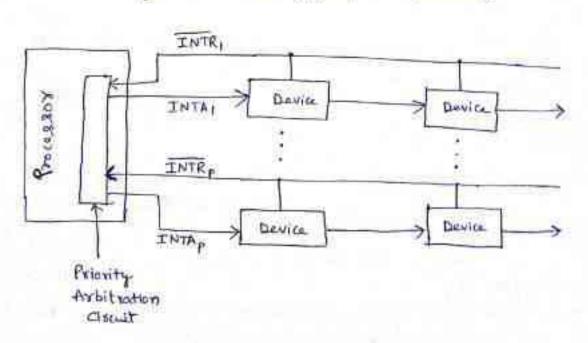

- -> The arrangement of priority groups is deficted as,

N

- -> Here, Devices are organized in groups, and each group is connected at a st different priority level.

- -> Within a group, devices are connected in a daisy-chain

- -> This organization is used in many computer systems.

(3) DMA: (Direct Hemory Acces)

- To transfer large blocks of data at high speed, a special control unit may be provided to allow transfer of a block of data directly between an external device and the main memory, without continuous intervention by the processor.

- -> This approach is called Direct Memory Access (DMA)

- -> DMA transfers are performed by a control unit that is part of the Ifo device interface, called DMA controllers.

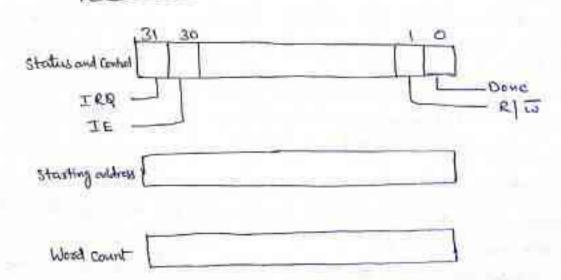

#### (\*) DMA controller,

- -> The DMA controller performs the functions that would normally be corried out by the processor when according the main memory.

- -> For each word transferred, it provides the memory address and all the but signals that are contain data transfer.

- -> Although the DMA controller can transfer data without intervention by the processor, its operation must be under the control of a program executed by the processor.

- -> The Registers used in DMA Controllers are depicted as,

# -> The use of BHA Controllers in a computer System is depicted as,

4.5

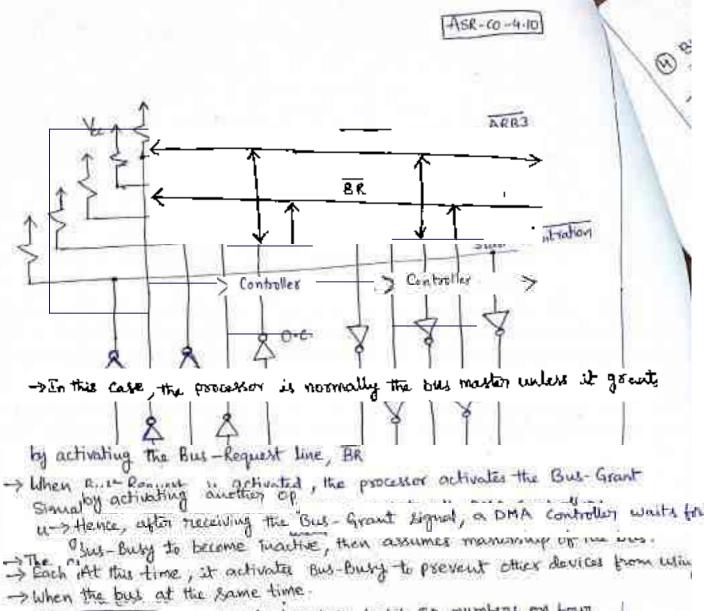

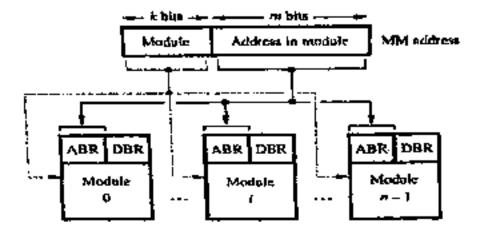

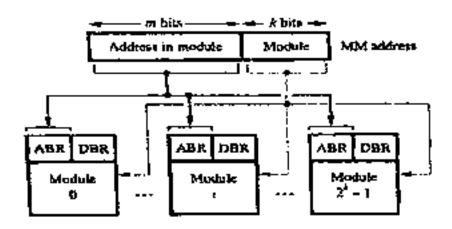

#### (#) Bus Arbitration .

- -> The device that is allowed to initiate data transfers on the bus at any given time is called the Bus Houston.

- -> But collitization is the process by which the next device to become the bus markership is transferred to it

- -> The Selection of the bus master must take into account the needs of various devices by establishing a provity system for gaining access to the bus.

- -> There are two approaches to bus asbit ration

- (i) Centralized Athitration

- (li) Distributed Arbitration

#### (i) Centralized Adoitration:

- -> In this approach, a single bus arbiter performs the negurinal assistration.

- -> A simple arrangement + for bus arbitration using a clairly chain is depicted as

Stant-Ashitsation sinual and place their 4-bit ID numbers on form dry W. Ctcir & Jzy4-bit "^i" Hugh ARE3

-> A winner is selected as a result of the interaction among the signals transmitted over these lines by all contenders.

-> The \_> Distributed arbitration means that all devices waiting to use the bus nequest that has the highest ID number.

# (4) BUSES.

- -The processor, main memory, and Ito devices can be interconnected by means of a Common bus.

- -> The Bus primary function is to provide a communication path for the transfer of data.

- -> The bus includes the lines needed to support interrupts and arbitration.

- -> The bus lines used for transferring data may be grouped into three types.

- data lines

- address lived

- In any data transfer operation, one device plays the note of a macter.

- This is the device that initiates data transfers by issuing read (or) write Commands on the but, hence, it may be called an initiator.

- Normally, the processor (00) devices with DMA capability become

- The device addressed by the marter is greferred to as a Blave (on target

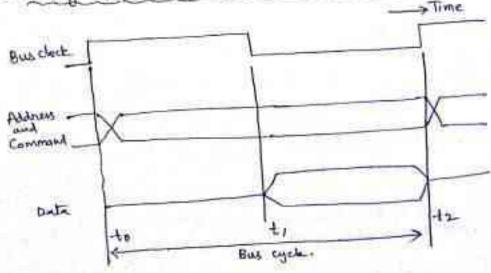

# (i) Synchronous Bus;

- In a synchronous bus, all devices derive timing information from a Common clock line.

- Equally spaced pulses on this line define equal time intervals.

- In the Simplest form of a synchronous bus, each of these intervals constitutes a bus cycle during which one data transfer can take place.

- Timing of an input transfer on a Synchronous bus is depicted as

> -> The address and datalines are high and low at the same-time.

-This is a common convention indicating that some lines are high and the some low, depending on the particular address (or) data pattern being transmitted.

-> The cooling points indicate the times at which these patterns change,

- -> A signal line is an indeterminate (or) high-impedance state is sepresented by an intermediate level half-way between the low and high signal levels.

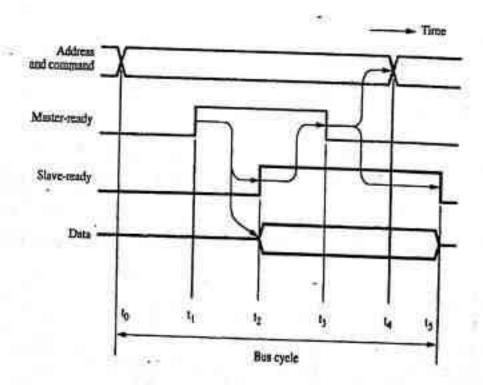

## (li) Asynchronous Bus;

- An alternative scheme for controlling data transfer on the but is based on the use of a handshake between the muster and the slave.

- -> Handshake control of data transfer during an input operation is deficted as

-> The Common clock is neplaced by two timing control lines - Master-Ready - Slave-Ready

- The first is asserted by the martin to indicate that it is needy for a transaction, and the second is a nesponse from the share.

-> In principle, a data transfer controlled by a handshake proceeds

- The master places the address and command information on the bus,

- Then it indicates to all devices that it has done so by activating the Marter-ready line-

7+14

- This causes all devices on the bus to decode the address. data and control.

- -> The master waits for Slave-nearly to become assented before to transfer data between the interface and the specific and

- -> This is called a post.

- -> It can be classified as

- is Parallel Post

- (ii) Serial Post

- -> A parallel post transfer data in the fam of a number of bits, typically 8 ps) 16, simultaneously to bis from the device.

- -> A Sexial post transmits and specious data one bit at a time

- -> Communication with the bus is the same for both formate, the conversion from the parallel to the serial format, and vice versa, takes place inside the interface circuit.

#### (i) Parallel Post,

COMMITTED

-> The related slave strobes the data juto its output buffer when it receives peripherals.

the Shore-ready signal to 1.

-> The remainder of the cycle is identical to the input operation.

Distriction

-> The DATAOUT YES drivers that are composed by a data current

ree-state DDR.

- -> For a given bit, it the DDR value is 1, the corresponding datalines acts as an output line, otherwise, it acts as an input line.

- -> Two lines C1 and C2, one provided to control the Interaction between the interface circuit and the I/o device it lerves.

- -> Line CZ is bidirectional to provide several different modes of signaling, including the handshake.

- -> The Ready and Accept lives are the handshake control lives on the processor bus side, and hence would be connected to Muster-ready and Slave-really

- -> The input silly sides output of sel to the an address Status **P.\$0** interface. control r.W -> An interrup Ready -> It should ! ow the computer be

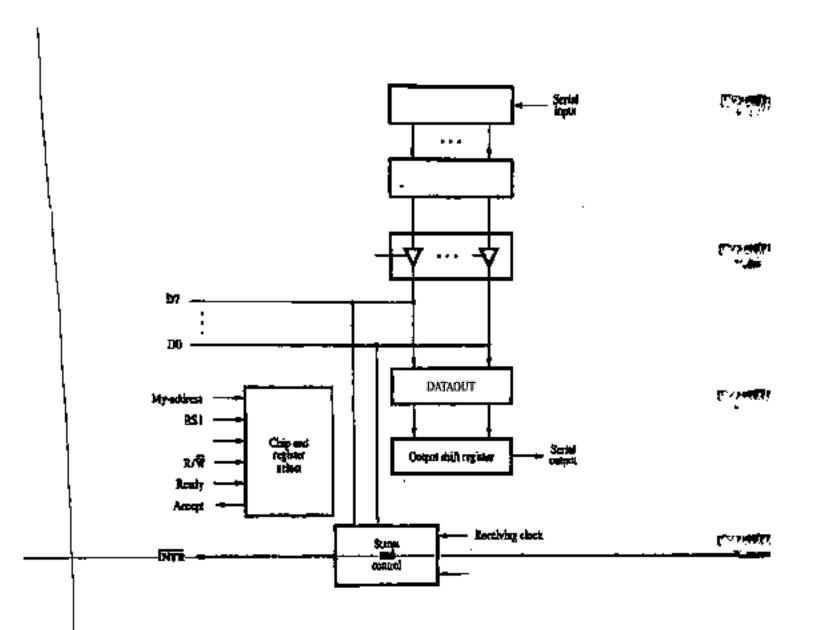

## (ii) Sexial Post.

- -> A serial port is used to connect the processor to Ito devices that trequire transmission of dala one bit at a time.

- -> The key feature of an interface circuit for a serial post is that it is Capable of Communicating in a bit-social fashion on the device side and in a bit-parallel fashion on the bus side.

- -> The transformation between the parallel and serial formate is achieved with shift registers that have parallel access capability.

- -> A Serial interface is depicted as,

III T

-> It includes the familian DATAIN and DATAOUT negisters.

-> when all 8 bits of data have been necesived, the condents of this

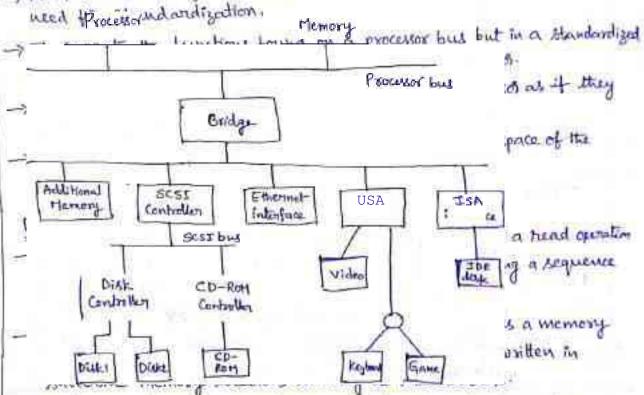

@ Standard I o Interfaces:

-> A different interface may have to be du of I/o device and computer, negulting → ISA - Industry Standard Architecture IDE - Integrated Device Electronics

-> The PCI standards defines an expansion but on the motherboard.

-> The two buses are interconnected by a circuit, which we will call a bridge, that translates the signals and protocols of one bus into

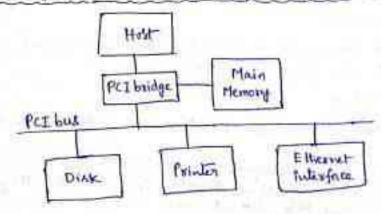

(i) PCI (Peripheral Component Interconnect) Bus:

-> The PCI bug is a great example of a system bus that grewout of the

-> The PCI is designed primarily to support this mode of operation.

-> A read (or) write operation involving a single word is simply treated as a burst of length one.

-> The use of a PCI bus in a Computer System is deficted as

help)

# (li) SCSI Bus ;

- SCSI strands to Small Computer System Interface.

- -> It refers to a standard bus defined by the ANSI (American National Standards Institute) under the designation X3.121

- → In the original specifications of the standard, devices such as disks are connected to a computer via a 50-wire cable, which can be upto 25 meters in length and can transfer data at reales up to 5 megabytes/5

- -> A SCSI bus may have & datalines, in which case it is called a warrow bus and transfers data one byte at a time.

- -> A wide Sc SI bus has 16 data lines and transfers data 16-bits at a time.

- -> The SCSI bus standard has undergone many revisions, and its data transfer capability has increased very rapidly, almost doubling every two years.

- -> SCSI-2, SCSI-3 have been defined, and each has Several options.

- -> The different SCSI bus signeds abe

- DIS ( Dotalius)

- DB(1) (Parity bit for the data bus)

- BSY (Busy)

- SEL (Selection)

- -clo (control/Deta)

- MSG (Merrage)

- REQ (Request)

- -ACK (Acknowledge)

- Ilo (Imput/output)

- ATN (Attention)

- RST (Reset)

# (11) USB (Universal Serial Bus):

- -> A simple, low-cost mechanism to connect the devices to the computer is possible using USB.

- -> The USB Supports two speeds of operation

- \* Low-Apred (1.5 Hb/s)

- # Full-liped (12 Hb/s)

- -> The recent development is USB 2.0

- -> The USB has been designed to meet several key objectives.

- provide a simple, low-cost, and easy to use interconnection

- Accommodate a wide mange of data transfer characteristics for I/o devices, including telephone and Internet Connections.

- Enhance user convenience through a "plug-and-play" mode of

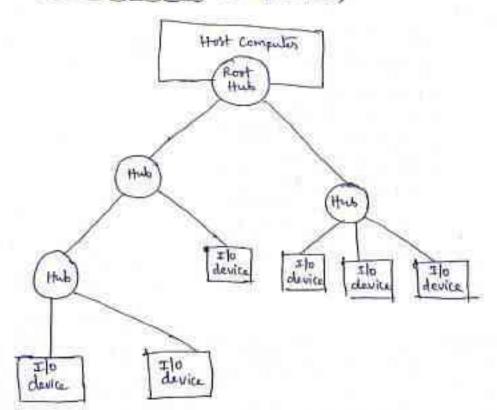

- -> USB Tree structure is depicted as,

- -> To accommodate a large number of devices that can be added (or) removed at any time, the USB has the tree structure.

- -> Each node of the tree has a device called a hub, which acts as an intermediate control point between the host and the I/o devices.

- -> At the root of the tree, a root hub connects the entire tree to the

- -> The leaves of the tree are the Ilo devices being served (for example, Keybrard, Internet connection, Speaker (1) digital TV), which are called functions in USB terminology.

#### USB protocols;

- All information transferred over the USB is organized in packets, where a packet consists of one (or) more lyter of information.

- -> The information divided transferred on the USB can be divided into

- Control

- -> Control packets perform such tasks as addressing a device to initiate data transfer, acknowledging that data have been received correctly, (or) indicating error.

- -> Data packets carry information that is delivered to a device.

- A packet contains one or more fields with different Kinds of Information.

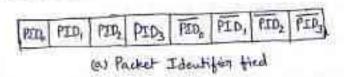

- -> The first field of any packet is called the packet identifier, PID, which identifies the type of that packet

- -> USB packet formats is depicted as,

PID

| Bita | 8   | 1 7             | 1 4     | 5     |

|------|-----|-----------------|---------|-------|

| ſ    | PID | APPR            | ENDP    | CRCIL |

| 1    | (6) | Token Packet, I | 1000 Oc | ۲     |

| Bita | 9 ( | 0 to 8192       | 1       | 16    |

DATA

ec) Data packet

-> ADDR - Address

ENDP - Ending Packet

CRC - Cyclic Redundancy Stor Check

#### Isochronous Traffic on USB:

- -> One of the key objectives of the USB is to suppost the transfer of Isochronous dala, such as sample voice, in a simple manner.

- -> Devices that generate (bx) receive blockronous data require a time reference to control the sampling process.

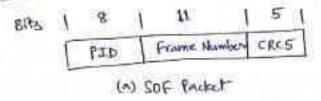

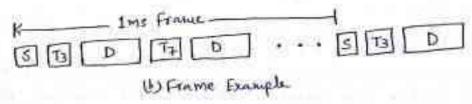

- -> To provide this greference, transmission over the USB is divided into frames of equal length.

- -> A frame is 1 ms long for full and low speed data.

- -> The 900t hub generated a Start of Frame (SOF) control packet precisely once every 1 ms to mark the beginning of a new frame.

- -> USB frames depicted as,

# Electrical characteristics,

- -) The cubbs used for USB connections consists of brust wines Two are used to carry power, +5V and Ground.

- The other two wires are used to carry data

# CO-UNITY - Short Answer Questions

- 1 Discuss about Single bus structure. Page 4.1

- 2) Explain about Memory-Mapped I/o. Page 4. L

- (3) What is programmed I/0? Programmed Ilo:

- -> Programmed I/o is a method of transferring data between the CPU and a peripheral.

#### Advantages:

- -> If a command is issued by the processor to the respective I/o module.

- -> Requested I/o instruction is executed at the earliest.

- -> Ifo module switches to the vext task as soon as it completes the fast.

- Disadvantages: -> Processor has to wait will the I/O module is ready for performing

- -> Processor have to Interrogate several times regarding the status of I/o module.

- @ what is interrupt -initiated data transfer ? Interrupt-initiated Data transfers:

- when the I/O device is nearly to transfer data, instead CPU keep asking, does not check the flag

- -> when the flag in the Interface is set, the interface will initiale an interrupt, and the CPU will drops what it is doing and do the

- -> Until The I/O transfer is done, it returns to what it was doing

- Franchos of control through the use of Interrupts is deficted as,

- 3 Discuss Daisy-chain priority Interrupt page 4-6

- @ Explain a) Interrupt b) Exception

- a) page 4.3

- b) Exception:

- -> An exception is an abnormal by unusual termination

- -> An exception is a condition that sugults from activate and prevents the processor from executing the convent instruction stream.

- -> It affects the normal execution of an instruction.

- ( What is DMA? page 4-7

- (8) What is the need for Bus Arbitration? page 4-8

- 1 Discuss handshaking (or) Asynchronous Data transfer (or) Asynchronous Ens page 4-12

- (10) Explain PCI bus. page 4.19

- (11) Explain SCSI bus. page 4.21

Mr Va Co

(2) Explain USB. page 4.12

# DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING. SIR C R REDDY COLLEGE OF ENGINEERING DE DEEPAK NEDUNURI

ELURU.

# COMPUTER ORGANIZATION UNIT-5: THE MEMORY SYSTEMS

#### Syllabus:

- Basic memory concepts

- Memory System Consideration

- Read- Only Memory

- ROM

- PROM

- EPROM

- EEPROM

- Flash Memory

- Cache Memories

- Mapping Functions

- INTERLEAVING

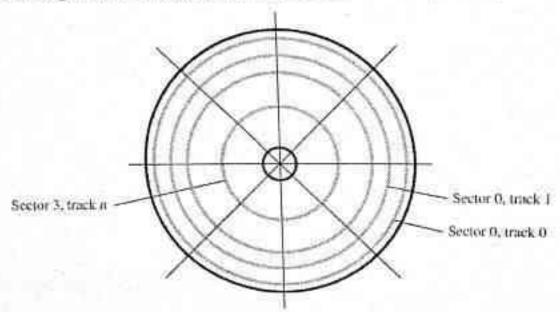

- Secondary Storage

- Magnetic Hard Disks

- Optical Disks

#### Text Book to Follow:

Computer Organization, Carl Hamacher, ZvonksVranesic, SafeaZaky, 5th Edition, McGraw Hill

#### 1. BASIC MEMORY CONCEPTS:

- A memory unit is the collection of storage units or devices together.

- The memory unit stores the binary information in the form of bits.

- Memory/ Storage is classified into 2 categories:

- i) Volatile Memory

- ii) Non Volatile Memory

#### i) Volatile Memory;

- This loses its data, when power is switched off.

#### ii) Non-Volatile Memory:

- This is a permanent storage and does not lose any data when power is switched off.

#### Memory Access Methods:

i) Random Access:

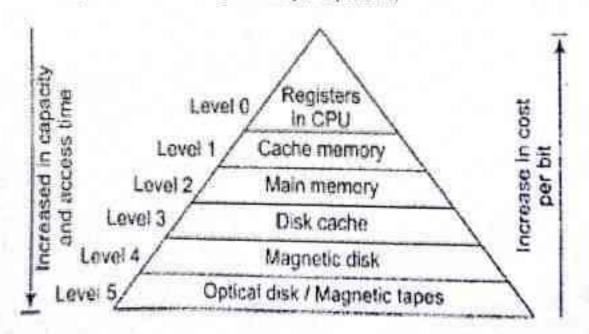

## Memory Hierarchy:

- The Memory Hierarchy is depicted as,

- The comparisons in the Memory Hierarchy is depicted as,

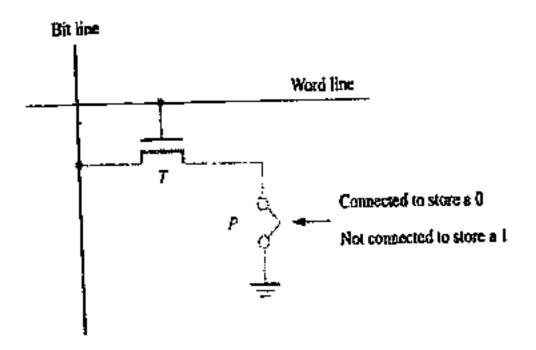

- A logic value 0 is stored in the cell if the transistor is connected to ground at point P, otherwise a 1 is stored.

- The bit line is connected through a resistor to the power supply

- -To read the state of the cell, the word line is activated

- Thus the transistor switch is closed and the voltage on the hit line drops to near zero if there is a connection between the transistor and ground.

- If there is no connection to ground, the bit line remains at the high voltage, indicating a 1.

- A sense circuit at the end of the bit line generates the proper output value.

- Data are written into a ROM when it is manufactured.

## PROM:

- It stands for Programmable Read Only Memory.

- It was first developed in 70s by Texas Instruments.

- It is made as a blank memory.

- A PROM programmer or PROM burner is required in order to write data onto a PROM chip.

- The data stored in it cannot be modified and therefore it is also known as one time programmable device.

INTLIK-RIS-2-2-CSE

5

#### EPROM:

- It stands for Erasable Programmable ROM.

- It is different from PROM as unlike PROM the program can be written on it more than once.

- This comes as the solution to the problem faced by PROM.

- The bits of memory come back to 1, when ultra violet rays of some specific wavelength falls into its chip's glass panel.

- The fuses are reconstituted and thus new things can be written on the memory.

#### EEPROM:

- It stands for Electrically Erasable Read Only Memory.

These are also erasable like EPROM, but the same work of erasing is performed with electric current. Thus, it provides the ease of erasing it even if the memory is positioned in the computer.

It stores computer system's BIOS. Unlike EPROM, the entire chip does not have to be erased for changing some portion of it.

- Thus, it even gets rid of some biggest challenges faced by using EPROMs.

#### FLASH ROM:

It is an updated version of EEPROM.

In EEPROM, it is not possible to after many memory locations at the same time. However, Flash memory provides this advantage over the EEPROM by enabling this feature of aftering many locations simultaneously.

It was invented by Toshiba and got its name from it capability of deleting a block of data in a flash.

#### Flash Cards:

- One way of constructing a larger module is to mount flash chips on a small card.

- Such flash cards have a standard interface that makes them usable in a variety of products.

- A card is simply plugged into a conveniently accessible slot.

- Flash cards come in a variety of memory sizes.

- Typical sizes are 8, 32, and 64 Mbytes.

#### Flash Drives:

Larger flash memory modules have been developed to replace hard disk drives.

- These flash drives are designed to fully emulate the hard disks, to the point that they can be fitted into standard disk drive bays.

- However, the storage capacity of the flash drives is significantly lower.

- Currently, the capacity of flash drives is less than one Giga Byte.

## 3. MEMORY SYSTEM CONSIDERATIONS:

- The choice of a RAM chip for a given application depends on several factors such as, cost, speed, power dissipation, and size of the chip.

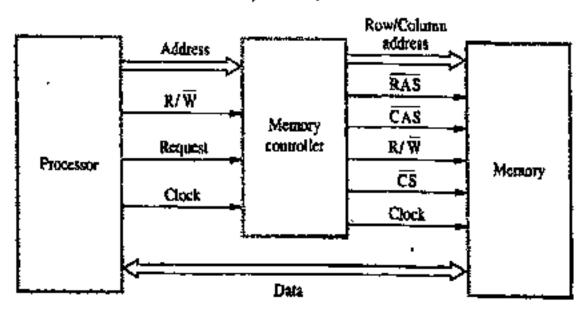

### Memory controller:

- The address is divided into two parts.

- The high-order address bits, which select a row in the cell array, are provided first and latched into the memory chip under control of the RAS signal.

- Then the lower-order address bits, which select a column, are provided on the same address pins and latched using the CAS signal.

- A typical procedure issues all bits of an address at the same time.

- The required multiplexing of address bits is usually performed by a Memory Controller Circuit, which is interposed between the processor and the dynamic memory

- Use of a Memory Controller is depicted as,

- The controller accepts a complete address and the R/W signal from the processor, under control of a request signal which indicates that a memory access operation is needed.

- The controller then forwards the row and column portions of the address to the memory and generates the RAS and CAS signals.

- Thus, whenever one of the main memory blocks 0, 128, 256, ... is loaded into the cache, it is stored in cache block0.

- Blocks 1, 129, 257. . . , are stored in cache block 1, and so on.

- The memory address can be divided into three fields

- The low-order 4 bits select one of 16 words in a block.

- When a new block enters the cache, the 7-bit cache block field determines the cache position in which this block must be stored.

- The high-order 5 bits of the memory address of the block are stored in 5 tag bits associated with its location in the cache.

- The tag bits identify which of the 32 main memory blocks mapped into this cache position is currently resident in the cache.

- As execution proceeds, the 7-bit cache block field of each address generated by the processor points to a particular block location in the cache.

- The high-order 5 bits of the address are compared with the tag bits associated with that eache location. If they match, then the desired word is in that block of the cache.