## SIR C.R.REDDY COLLEGE OF ENGINEERING ELURU – 534007

## DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

## DIGITAL ELECTRONICS & MICROPROCESSOR LAB MANUAL

## 2/4 CSE: II- SEMESTER

**Faculty:**

B.Homer Benny (Section-'A')S.K.Chaitanya.R (Section-'B')S.Jaya Prakash (Section-'C')

## **DIGITAL ELECTRONICS & MICROPROCESSOR LAB**

## 2/4 CSE: II - SEMESTER

## **INDEX**

| S.No | Name of the Experiment                                                          | Page<br>Number |

|------|---------------------------------------------------------------------------------|----------------|

| 1.   | Study of basic gates.                                                           | 3              |

| 2.   | Realization of Gates by using Universal Building Blocks.                        | 5              |

| 3.   | Realization of Flip-Flops.                                                      | 9              |

| 4.   | 4-bit Ripple counter.                                                           | 11             |

| 5.   | 4-bit Shift Register.                                                           | 14             |

| 6.   | 4-bit & 8-bit Binary Adders                                                     | 17             |

| 7.   | Addition of two 8-bit numbers                                                   | 20             |

| 8.   | Subtraction of two 8 - bit numbers                                              | 23             |

| 9.   | Multiplication of two 8-bit numbers                                             | 26             |

| 10.  | Division of two 8-bit numbers                                                   | 29             |

| 11.  | Addition of two 16-bit numbers                                                  | 32             |

| 12.  | Subtraction of two 16 - bit numbers                                             | 35             |

| 13.  | BCD addition                                                                    | 38             |

| 14.  | BCD subtraction                                                                 | 42             |

| 15.  | Sorting of data in Ascending order and finding Largest<br>Number in the array   | 45             |

| 16.  | Sorting of data in Descending order and finding Smallest<br>Number in the array | 49             |

| 17.  | DAC/ADC interface                                                               | 53             |

| 18.  | Stepper motor controller                                                        | 57             |

| 19.  | 8279- programmable keyboard/display interface                                   | 61             |

#### EXPERIMENT: 1 STUDY OF BASIC GATES

AIM: To study and verify the truth table of logic gates

#### LEARNING OBJECTIVE:

• Identify various ICs and their specification.

#### **COMPONENTS REQUIRED:**

- Logic gates (IC) trainer kit.

- Connecting patch chords.

- IC 7400, IC 7408, IC 7432, IC 7406, IC 7402, IC 7404, IC 7486

#### THEORY:

The basic logic gates are the building blocks of more complex logic circuits. These logic gates perform the basic Boolean functions, such as AND, OR, NAND, NOR, Inversion, Exclusive-OR, Exclusive-NOR. Fig. below shows the circuit symbol, Boolean function, and truth. It is seen from the Fig that each gate has one or two binary inputs, A and B, and one binary output, C. The small circle on the output of the circuit symbols designates the logic complement. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative.

These basic logic gates are implemented as small-scale integrated circuits (SSICs) or as part of more complex medium scale (MSI) or very large-scale (VLSI) integrated circuits. Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. The following logic families are the most frequently used.

- TTL Transistor-transistor logic

- ECL Emitter-coupled logic

- MOS Metal-oxide semiconductor

- CMOS Complementary metal-oxide semiconductor

TTL and ECL are based upon bipolar transistors. TTL has a well established popularity among logic families. ECL is used only in systems requiring high-speed operation. MOS and CMOS, are based on field effect transistors. They are widely used in large scale integrated circuits because of their high

component density and relatively low power consumption. CMOS logic consumes far less power than MOS logic. There are various commercial integrated circuit chips available. TTL ICs are usually distinguished by numerical designation as the 5400 and 7400 series.

#### PROCEDURE:

- 1. Check the components for their working.

- 2. Insert the appropriate IC into the IC base.

- 3. Make connections as shown in the circuit diagram.

- 4. Provide the input data via the input switches and observe the output on output LEDs

| S.NO | GATE     | SYMBOL                              | INPU | TS | OUTPUT |

|------|----------|-------------------------------------|------|----|--------|

|      |          |                                     | A    | В  | С      |

| 1.   | NAND IC  |                                     | 0    | 0  | 1      |

|      | 7400     | $A$ $C=\overline{AB}$               | 0    | 1  | 1      |

|      |          | B                                   | 1    | 0  | 1      |

|      |          |                                     | 1    | 1  | 0      |

| 2.   | NOR IC   | 5                                   | 0    | 0  | 1      |

|      | 7402     | A $C = \overline{A} + \overline{B}$ | 0    | 1  | 0      |

|      |          | в                                   | 1    | 0  | 0      |

|      |          |                                     | 1    | 1  | 0      |

| 3.   | AND IC   |                                     | 0    | 0  | 0      |

|      | 7408     | AC=AB                               | 0    | 1  | 0      |

|      |          | В                                   | 1    | 0  | 0      |

|      |          |                                     | 1    | 1  | 1      |

| 4.   | OR       |                                     | 0    | 0  | 0      |

|      | IC 7432  | A                                   | 0    | 1  | 1      |

|      |          | в) )                                | 1    | 0  | 1      |

|      |          |                                     | 1    | 1  | 1      |

| 5.   | NOT      | AC=Ā                                | 1    | (  | 0      |

|      | IC 7404  |                                     | 0    | 12 | 1      |

| 6.   | EX-OR IC | 10-                                 | 0    | 0  | 0      |

|      | 7486     | 1                                   | 0    | 1  | 1      |

|      |          | A)) )                               | 1    | 0  | 1      |

|      |          | BC=AB+BA                            | 1    | 1  | 0      |

#### EXPERIMENT: 2 REALIZATION OF GATES BY USING UNIVERSAL BUILDING BLOCKS

<u>Aim</u>: To Realize AND,OR,NOT,EX-OR and EX-NOR gates by using only NAND and only NOR gates

#### **Apparatus and Components :**

| S.No | Name            | Quantity |

|------|-----------------|----------|

| 1.   | Digital trainer | 1        |

| 2.   | IC 7400         | 2        |

| 3.   | IC 7402         | 2        |

#### **Procedure** :

#### **Using NAND Gates:**

- 1. Derive truth table

- 2. Realize expression of AND gate by using number of NAND gates

- 3. Connect the circuit

- 4. Verify the truth table

- 5. Repeat above steps for OR, NOT, EX-OR and EX-NOR gates

#### Using NOR Gates:

- 1. Derive truth table

- 2. Realize expression of AND gate by using number of NOR gates

- 3. Connect the circuit

- 4. Verify the truth table

- 5. Repeat above steps for OR, NOT, EX-OR and EX-NOR gates

#### Result :

Basic gates are realized by using Universal building blocks.

#### **<u>Circuit Diagram</u>** :

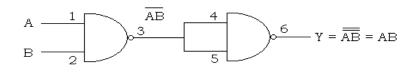

#### **Realization of AND gate using only NAND gates**

| A | В | Y = AB |

|---|---|--------|

| 0 | О | 0      |

| 0 | 1 | О      |

| 1 | 0 | Ο      |

| 1 | 1 | 1      |

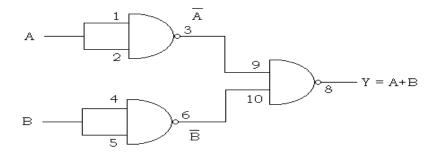

#### Realization of OR gate using only NAND gates

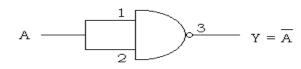

# Realization of NOT gate using only NAND gates

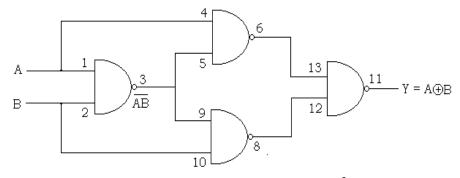

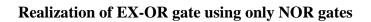

#### Realization of EX-OR gate using only NAND gates

| A | В | Y = A⊕B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

| А | В | Y =A+B |

|---|---|--------|

| 0 | 0 | Ο      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

| A | $Y = \overline{A}$ |

|---|--------------------|

| 0 | 1                  |

| 1 | 0                  |

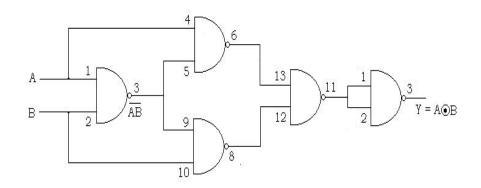

### Realization of EX-NOR gate using only NAND gates

# A B Y = A⊛B 0 0 1 0 1 0 1 0 0 1 1 1

A

B

Y = AB

0

0

0

0

1

0

1

0

0

1

1

1

## Realization of AND gate using only NOR gates

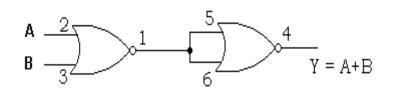

#### Realization of OR gate using only NOR gates

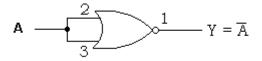

Realization of NOT gate using only NOR gates

| А | В | Y =A+B |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

| A | $Y = \overline{A}$ |

|---|--------------------|

| 0 | 1                  |

| 1 | О                  |

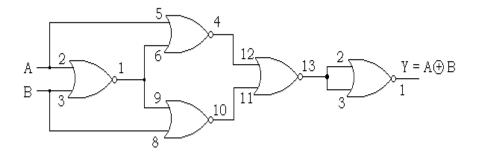

| A | В | Y = A⊕B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

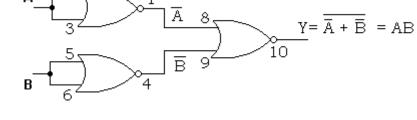

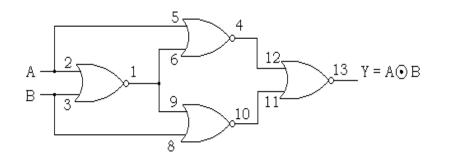

## Realization of EX-NOR gate using only NOR gates

| A | в | Y = A • B |

|---|---|-----------|

| 0 | 0 | 1         |

| 0 | 1 | 0         |

| 1 | 0 | 0         |

| 1 | 1 | 1         |

#### EXPERIMENT: 3 <u>REALIZATION OF FLIPFLOPS</u>

Aim : To Construct different types of flip-flops and verify the truth tables.

#### **Apparatus and Components :**

| S.No | Name            | Quantity |

|------|-----------------|----------|

| 1.   | Digital trainer | 1        |

| 2.   | IC 7476         | 1        |

| 3.   | IC 7400         | 1        |

| 4.   | IC 7404         | 1        |

#### **Procedure** :

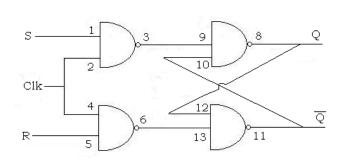

1. RS flip-flop is wired as shown in fig and input signals are fed from logic input switches and the output is monitored on the logic level output condition indicators and the truth table is verified.

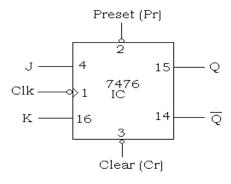

2. JK flip-flop is wired as shown in fig and the input signals are fed from logic input switches and the output is monitored on the logic level output condition indicators and the truth table is verified.

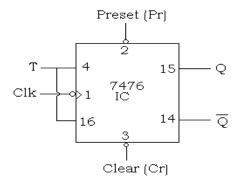

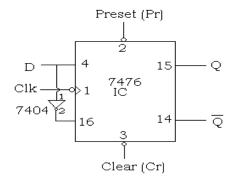

3. Verify the truth tables of D flip flop and T flip flop in the same procedure.

#### Result :

Truth tables of RS, JK, D and T flip-flops are verified.

#### **<u>Circuit Diagram</u>**:

#### **Realization of RS flip- flop using NAND gates**

| Clk | S | R | Theoretical      | Practical        |

|-----|---|---|------------------|------------------|

| CIK | 3 |   | Q <sub>n+1</sub> | Q <sub>n+1</sub> |

| 0   | Х | Х | Qn               |                  |

| 1   | 0 | 0 | Qn               |                  |

| 1   | 0 | 1 | 0                |                  |

| 1   | 1 | 0 | 1                |                  |

| 1   | 1 | 1 | ?                |                  |

#### <u>JK flip- flop</u>

|              | DD | CD | т | V | Theoretical     | Practical |

|--------------|----|----|---|---|-----------------|-----------|

| Clk          | PR | CR | J | K | Qn+1            | Qn+1      |

| 0            | 0  | 1  | Х | Х | 1               |           |

| 0            | 1  | 0  | Х | Χ | 0               |           |

| $\downarrow$ | 1  | 1  | 0 | 0 | Qn              |           |

| $\downarrow$ | 1  | 1  | 0 | 1 | 0               |           |

| $\downarrow$ | 1  | 1  | 1 | 0 | 1               |           |

| $\downarrow$ | 1  | 1  | 1 | 1 | $\overline{Qn}$ |           |

#### <u>T flip- flop</u>

|              | DD | CD | Т | Theoretical     | Practical |

|--------------|----|----|---|-----------------|-----------|

| Clk          | PR | CR | Т | Qn+1            | Qn+1      |

| 0            | 0  | 1  | Х | 1               |           |

| 0            | 1  | 0  | Х | 0               |           |

| $\downarrow$ | 1  | 1  | 0 | Qn              |           |

| $\downarrow$ | 1  | 1  | 1 | $\overline{Qn}$ |           |

#### <u>D flip- flop</u>

| CIL          | DD | CD | D | Theoretical | Practical |

|--------------|----|----|---|-------------|-----------|

| Clk          | PR | CR | D | Qn+1        | Qn+1      |

| 0            | 0  | 1  | Х | 1           |           |

| 0            | 1  | 0  | Х | 0           |           |

| $\downarrow$ | 1  | 1  | 0 | 0           |           |

| $\downarrow$ | 1  | 1  | 1 | 1           |           |

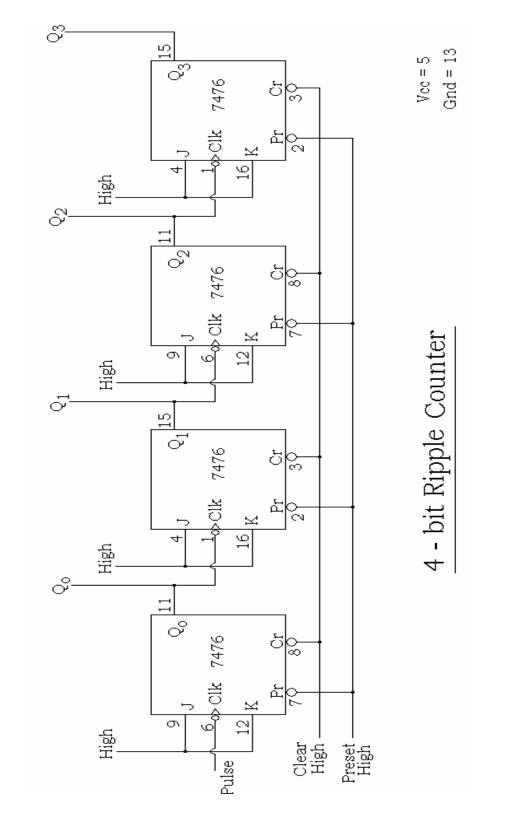

#### **EXPERIMENT: 4** <u>4-BIT RIPPLE COUNTER</u>

<u>Aim</u>: To design Asynchronous (Ripple) counter and verify the truth table.

#### **Apparatus and Components :**

| S.No | Name            | Quantity |

|------|-----------------|----------|

| 1.   | Digital trainer | 1        |

| 2.   | IC 7476         | 2        |

#### **<u>Procedure</u>** :

1. Ripple counter circuit is connected as shown in the circuit diagram.

2. 1Hz clock pulse is applied to the pin shown.

3. The outputs  $Q_0Q_1Q_2Q_3$  are observed and verify the truth table.

#### Result :

Asynchronous counter is constructed and truth table is verified.

## <u>4 – bit Ripple Counter Truth Table.</u>

| Clock pulses | Q3 | Q2 | Q1 | Q0 |

|--------------|----|----|----|----|

| 0            | 0  | 0  | 0  | 0  |

| 1            | 0  | 0  | 0  | 1  |

| 2            | 0  | 0  | 1  | 0  |

| 3            | 0  | 0  | 1  | 1  |

| 4            | 0  | 1  | 0  | 0  |

| 5            | 0  | 1  | 0  | 1  |

| 6            | 0  | 1  | 1  | 0  |

| 7            | 0  | 1  | 1  | 1  |

| 8            | 1  | 0  | 0  | 0  |

| 9            | 1  | 0  | 0  | 1  |

| 10           | 1  | 0  | 1  | 0  |

| 11           | 1  | 0  | 1  | 1  |

| 12           | 1  | 1  | 0  | 0  |

| 13           | 1  | 1  | 0  | 1  |

| 14           | 1  | 1  | 1  | 0  |

| 15           | 1  | 1  | 1  | 1  |

| 16           | 0  | 0  | 0  | 0  |

## <u>Circuit Diagram:</u>

13

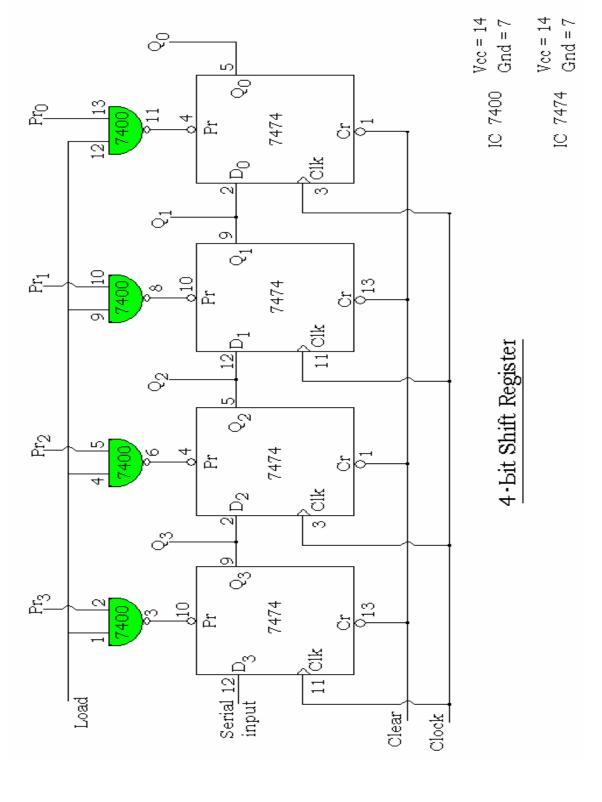

#### EXPERIMENT: 5 <u>4 - BIT SHIFT REGISTER</u>

<u>Aim</u>: To design 4-bit shift register and verify the operation of serial loading and parallel loading,

#### **Apparatus and Components :**

| S.No | Name            | Quantity |

|------|-----------------|----------|

| 1.   | Digital trainer | 1        |

| 2.   | IC 7474         | 2        |

| 3.   | IC 7400         | 1        |

#### **Procedure** :

- 1. Connect the circuit as shown in fig.

- 2. For serial loading keep load low.

- 3. First clear all the flip-flops by supplying clear = low

- 4. First enter serial input one by one, through clock pulse; we will get Parallel output at  $Q_3Q_2Q_1Q_0$ . After applying 4 clock pulses we will get serial output.

5. For parallel input keep load = high

6. Directly apply parallel input to  $P_{r3}$ ,  $P_{r2}$ ,  $P_{r1}$ ,  $P_{r0}$ ; we will get parallel output at  $Q_3Q_2Q_1Q_0$ . After applying 4 clock pulses we will get serial output.

**<u>Result</u>** : The operation of 4-bit shift register for serial loading and parallel loading is observed

## <u>4 – bit Shift Register Truth Table :</u>

| Load | Clk | Clear | Serial i/p |    | Paralle | Serial output Qo |    |   |

|------|-----|-------|------------|----|---------|------------------|----|---|

|      |     |       |            | Q3 | Q2      | Q1               | Q0 |   |

| 0    | Х   | 0     | Х          | 0  | 0       | 0                | 0  | 0 |

| 0    | 1   | 1     | 0          | 0  | 0       | 0                | 0  | 0 |

| 0    | 2   | 1     | 1          | 1  | 0       | 0                | 0  | 0 |

| 0    | 3   | 1     | 0          | 0  | 1       | 0                | 0  | 0 |

| 0    | 4   | 1     | 1          | 1  | 0       | 1                | 0  | 0 |

| 0    | 5   | 1     | 0          | 0  | 1       | 0                | 1  | 1 |

| 0    | 6   | 1     | 0          | 0  | 0       | 1                | 0  | 0 |

| 0    | 7   | 1     | 0          | 0  | 0       | 0                | 1  | 1 |

Serial Input → Serial Output / Parallel Output: The input is 1010.

## Parallel input $\rightarrow$ Parallel Output / Serial Output : The input is 1010.

| Load | Clk | Clear |     | Paral | lel i/p |     | ]  | Paralle | loutput |    | Serial<br>output |

|------|-----|-------|-----|-------|---------|-----|----|---------|---------|----|------------------|

|      |     |       | Pr3 | Pr2   | Pr1     | Pr0 | Q3 | Q2      | Q1      | Q0 | Qo               |

| 0    | X   | 0     | Х   | X     | Х       | X   | 0  | 0       | 0       | 0  | 0                |

| 1    | X   | 1     | 1   | 0     | 1       | 0   | 1  | 0       | 1       | 0  | 0                |

| 0    | 1   | 1     | Х   | X     | Х       | X   | 0  | 1       | 0       | 1  | 1                |

| 0    | 2   | 1     | Х   | Х     | Х       | Х   | 0  | 0       | 1       | 0  | 0                |

| 0    | 3   | 1     | X   | X     | Х       | X   | 0  | 0       | 0       | 1  | 1                |

#### **<u>Circuit Diagram</u>:**

16

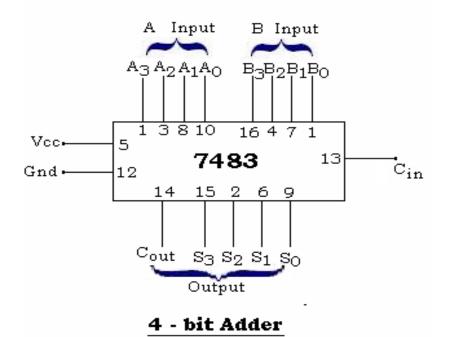

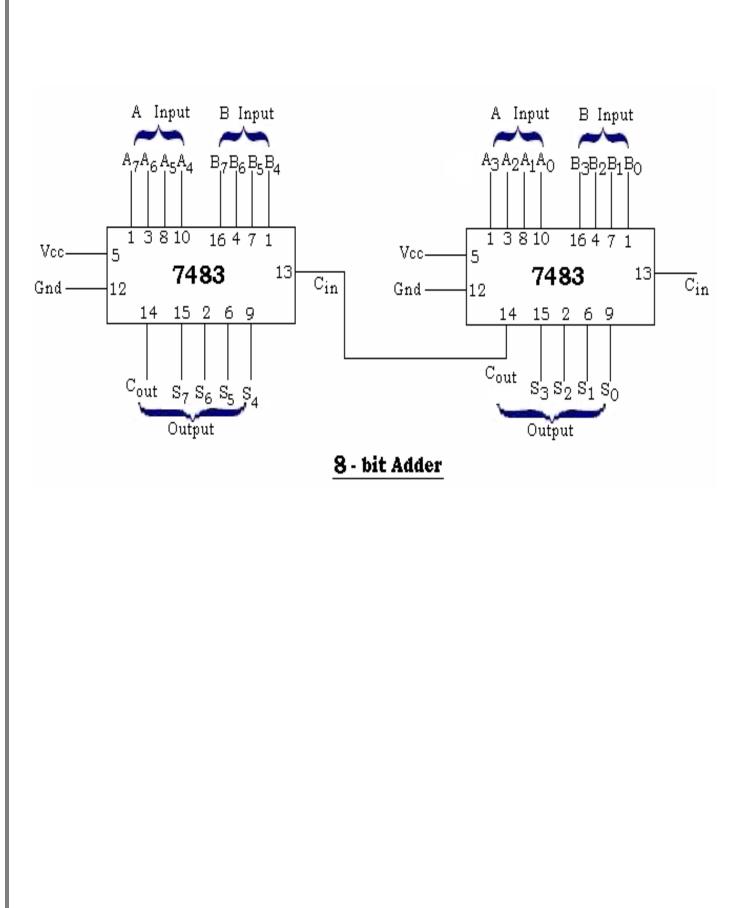

#### EXPERIMENT: 6 <u>4-BIT & 8-BIT BINARY ADDERS</u>

Aim : To construct and evaluate 4 bit and 8 bit adders

#### **Apparatus and Components :**

| S.No | Name            | Quantity |

|------|-----------------|----------|

| 1.   | Digital Trainer | 1        |

| 2.   | IC 7483         | 2        |

| 3.   | IC 7486         | 2        |

| 4.   | IC 7404         | 1        |

#### **Procedure** :

#### Adders:

- 1. The circuit is connected as shown in fig.

- 2. Apply two 4 bit positive numbers A and B, observe the output.

- 3. Verify the truth table.

- 4. Repeat above steps for 8 bit adders also.

#### Result :

The truth tables for 4 bit & 8 bit full adders are verified.

#### **Truth Table :**

#### <u>4 – bit Binary Adder :</u>

| A3 | <b>A</b> 2 | A <sub>1</sub> | Ao | <b>B</b> 3 | <b>B</b> <sub>2</sub> | <b>B</b> 1 | Bo | Cin | <b>S</b> 3 | <b>S</b> 2 | <b>S</b> 1 | S0 | Cout |

|----|------------|----------------|----|------------|-----------------------|------------|----|-----|------------|------------|------------|----|------|

|    |            |                |    |            |                       |            |    |     |            |            |            |    |      |

|    |            |                |    |            |                       |            |    |     |            |            |            |    |      |

|    |            |                |    |            |                       |            |    |     |            |            |            |    |      |

|    |            |                |    |            |                       |            |    |     |            |            |            |    |      |

|    |            |                |    |            |                       |            |    |     |            |            |            |    |      |

#### 8 – bit Binary Adder :

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | <b>B7</b> | <b>B6</b> | B5 | B4 | B3 | B2 | B1 | <b>B0</b> | Cin | <b>S7</b> | <b>S6</b> | S5 | <b>S4</b> | <b>S</b> 3 | S2 | <b>S1</b> | <b>S0</b> | Cout |

|----|----|----|----|----|----|----|----|-----------|-----------|----|----|----|----|----|-----------|-----|-----------|-----------|----|-----------|------------|----|-----------|-----------|------|

|    |    |    |    |    |    |    |    |           |           |    |    |    |    |    |           |     |           |           |    |           |            |    |           |           |      |

|    |    |    |    |    |    |    |    |           |           |    |    |    |    |    |           |     |           |           |    |           |            |    |           |           |      |

|    |    |    |    |    |    |    |    |           |           |    |    |    |    |    |           |     |           |           |    |           |            |    |           |           |      |

|    |    |    |    |    |    |    |    |           |           |    |    |    |    |    |           |     |           |           |    |           |            |    |           |           |      |

|    |    |    |    |    |    |    |    |           |           |    |    |    |    |    |           |     |           |           |    |           |            |    |           |           |      |

#### Circuit Diagram:

#### EXPERIMENT: 7 ADDITION OF TWO 8-BIT NUMBERS

#### **PROGRAM:**

Write an assembly language program to add two binary numbers of 8-bit data stored in memory locations 8C40H and 8C41H and store the result in 8C42H and 8C43H.

#### **PROBLEM ANALYSIS:**

To perform addition in 8085 one of the data should be in accumulator and another data can be in any one of the general purpose register or in memory. After addition the sum will be in accumulator. The sum of two 8-bit data can be either 8-bit (sum only) or 9 bits (sum and carry). The accumulator can be accommodated only the sum and if there is a carry, the 8085 will indicate by setting carry flag. Hence one of the register is used to account for carry.

#### **ALGORITHM:**

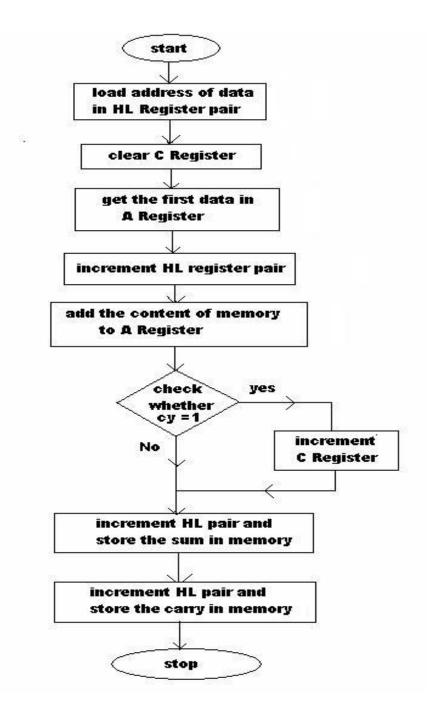

- 1. Load the address of the data in H L reg. pair.

- 2. Clear C register.

- 3. Move the first data from memory to accumulator.

- 4. Increment the H L register pair (memory pointer).

- 5. Add the content as memory addressed by H L with accumulator.

- 6. Check for carry. If carry=1, go to step 7 or if carry =0, go to step 8.

- 7. Increment the C register.

- 8. Increment the H L pair and store the sum.

- 9. Increment the H L pair and store the carry.

- 10. Stop.

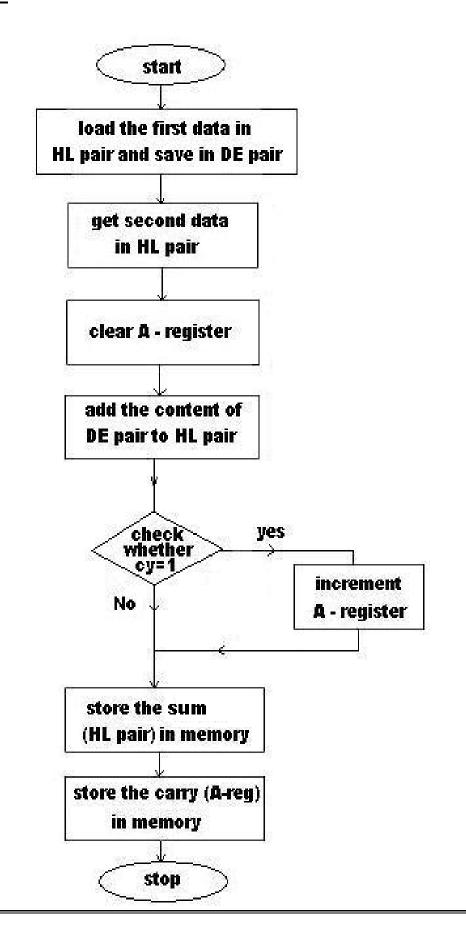

#### **FLOWCHART:**

#### ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE<br>CODE | LABEL | MNEMONIC    | COMMENT                               |

|--------------------|-----------------|-------|-------------|---------------------------------------|

| 8C00H              | 21 40 8C        |       | LXI H, 8C40 | OH // Set pointer for data.           |

| 8C03H              | 0E 00           |       | MVI C,00H   | // Clear C Reg. to account for        |

|                    |                 |       |             | carry                                 |

| 8C05H              | 7E              |       | MOV A,M     | // Get first data in A reg.           |

| 8C06H              | 23              |       | INX H       | // Increment the pointer for          |

|                    |                 |       |             | second data                           |

| 8C07H              | 86              |       | ADD M       | // Add second data which is stored in |

|                    |                 |       |             | memory to A. sum in A Reg.            |

| 8C08H              | D2 0C 8C        |       | JNC L1      | // if CY=0, go to <b>L1</b>           |

| 8C0BH              | 0C              |       | INR C       | // if CY=1 increment register C       |

| 8C0CH              | 23              | L1:   | INX H       | // increment the pointer to store the |

|                    |                 |       |             | sum in Memory                         |

| 8C0DH              | 77              |       | MOV M,A     | // Store the sum in memory.           |

| 8C0EH              | 23              |       | INX H       | // Increment the pointer to store the |

|                    |                 |       |             | carry in Memory.                      |

| 8C0FH71            |                 |       | MOV M,C     | // Store the carry in memory          |

| 8C10H76            |                 |       | HLT         | // Halt the program                   |

#### **OUTPUT:**

8C40::02

8C41::03

8C42::05

8C43::00

#### EXPERIMENT: 8 SUBTRACTION OF TWO 8 - BIT NUMBERS

#### **PROGRAM:**

Write an assembly language program to subtract two numbers of 8-bit data stored in memory locations 8C40H and 8C41H. Store the magnitude of the result in 8C42H. If the result is positive store 00 in 8C43H or if the result is negative store 01in 8C43H.

#### **PROGRAM ANALYSIS:**

To perform subtraction in 8085 one of the data should be in accumulator and another data can be in anyone of the general purpose register or in memory. After subtraction the result will be in accumulator. The 8085 performs 2's complement subtraction and then complements the carry. Therefore if the result is negative then carry flag is set and accumulator will have 2's complement of the result. Hence one of the register is used to account for sign of the result. To get the magnitude of the result again take 2's complement of the result.

#### **ALGORITHM:**

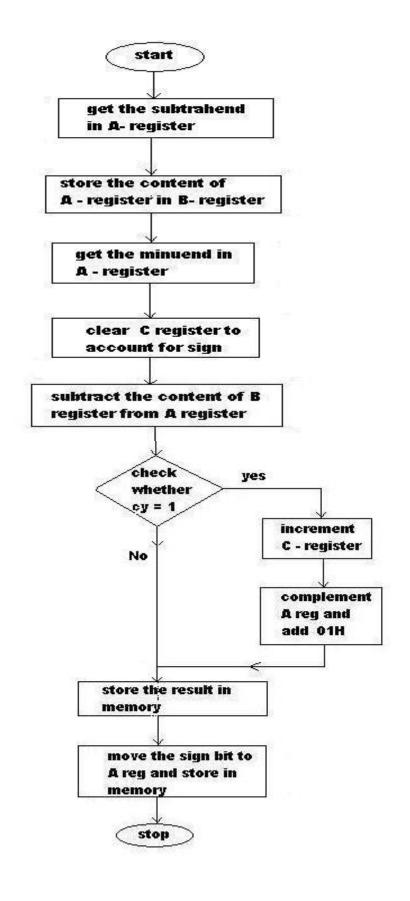

- Load the subtrahend (the data to be subtracted) from memory to accumulator and move it to B- register.

- 2. Load the minuend from memory to accumulator.

- 3. Clear C register to account for sign of the result.

- 4. Subtract the content of B-register from the content of the accumulator.

- 5. Check for carry . if carry =1 go to step 6 or if carry=0, go to step 7.

- 6. Increment C register, complement the accumulator and add 01H

- 7. store the difference in memory.

- 8. Move the content of C register (sign bit) to accumulator and store in memory.

- 9. Stop.

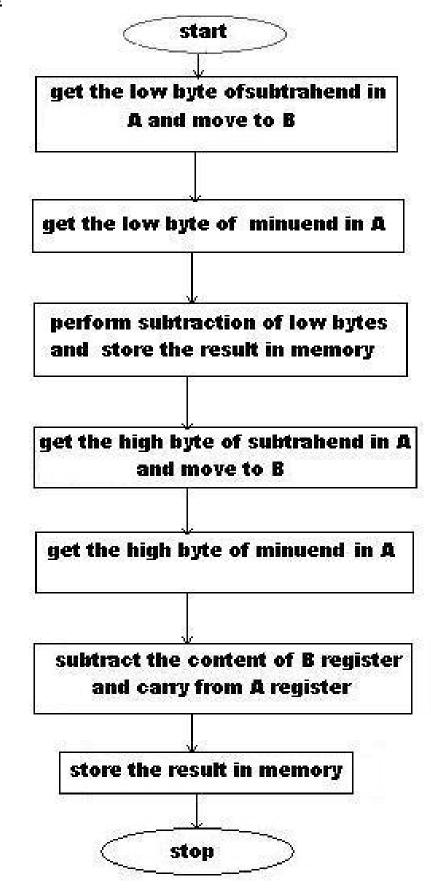

#### **FLOWCHART:**

#### ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE LABE | L MNEMONIC | COMMENT                                      |

|--------------------|--------------|------------|----------------------------------------------|

| 8C00H              | 3A 41 8C     | LDA 8C41H  | ; get subtrahend from 8C41H and store in Acc |

| 8C03H              | 47           | MOV B,A    | ; move the content of the Acc. into B reg.   |

| 8C04H              | 3A 40 8C     | LDA 8C40H  | ; get the minuend in A - reg                 |

| 8C07H              | 0E 00        | MVI C,00H  | ; clear C register , to account for sign.    |

| 8C09H              | 90           | SUB B      | ; get the difference in A register           |

| 8C0AH              | D2 11 8C     | JNC L1     | ; if $CY = 0$ , then go to L1                |

| 8C0DH              | 0C           | INR C      | ; if $CY = 1$ then increment C register.     |

| 8C0EH              | 2F           | СМА        | ; get 2's complement of difference           |

|                    |              |            | in A-reg                                     |

| 8C0FH              | C6 01        | ADI 01     | ; increment A register                       |

| 8C11H              | 32 42 8C L1  | STA 8C42H  | ; store the result in memory                 |

| 8C14H              | 79           | MOV A,C    | ; move the barrow to accumulator             |

| 8C15H              | 32 43 8C     | STA 8C43H  | ; store the sign bit in memory.              |

| 8C18H              | 76           | HLT        | ; halt the program                           |

| OUTPUT:            |              |            |                                              |

8C40::02 8C41::03 8C42::01

8C43::01

## EXPERIMENT: 9 <u>MULTIPLICATION OF TWO 8-BIT NUMBERS</u> PROBLEM:

Write an assembly language program to multiply two numbers of 8–bit data stored in memory 8C4OH and 8C41H. Store the product in 8C42H and 8C43H.

#### **PROBLEM ANALYSIS:**

In this method multiplication is performed as repeated additions. The initial value of sum is assumed as zero. One of the data is used as count (N). For number of additions to be performed. Another data is added to the sum N times where N is the count. The result of the product of two 8-bit data may be 16-bit data. Hence another register is used to account for over flow.

#### **ALGORITHM:**

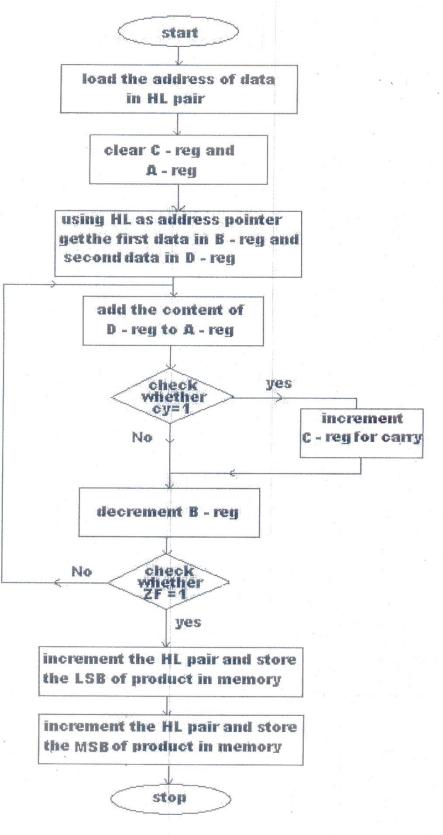

- 1. Load the address of the first data in H L pair.

- 2. Clear C register for over flow.

- 3. Clear the accumulator.

- 4. Move the first data to B register.

- 5. Increment the pointer.

- 6. Move the second data to D register from memory.

- 7. Add the content of D-register to accumulator.

- 8. Check for carry. If CY=1 go to step 9 or if CY=0 go to step10.

- 9. Increment C register.

- 10. Decrement B register.

- 11. Check whether count has reached zero. If ZF=0 repeat steps 7 to 11. if ZF=1 got to next step.

- 12. Increment the pointer and store the LSB of the product in memory.

- 13. Increment the pointer and store the MSB of the product in memory.

- 14. Stop.

#### **FLOWCHART:**

#### ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE<br>CODE | LABEL | MNE | MONIC    | COMMENT                          |

|--------------------|-----------------|-------|-----|----------|----------------------------------|

| 8COOH              | 21 40 8C        |       | LXI | H, 8C40H | ; set pointer for data.          |

| 8CO3H              | 0E 00           |       | MVI | C, OOH   | ; clear C register to account    |

|                    |                 |       |     |          | for over flow                    |

| 8CO5H              | AF              |       | XRA | А        | ; clear accumulator              |

|                    |                 |       |     |          | (initial sum=0).                 |

| 8CO6H              | 46              |       | MOV | B,M      | ; get first data in B register.  |

| 8C07H23            |                 |       | INX | Н        | ; increment pointer.             |

| 8CO8H              | 56              |       | MOV | D,M      | ; get second data in D register. |

| 8CO9H              | 82              | L1    | ADD | D        | ; add the content D register to  |

|                    |                 |       |     |          | accumulator                      |

| 8COAH              | 02 0E 8C        |       | JNC | L2       | ; if CY=0, go to L2              |

| 8CODH              | 0C              |       | INR | С        | ; if CY=1 increment C register   |

| 8COEH              | 05              | L2    | DCR | В        | ; if CY=0 decrement B register   |

| 8COFH              | C2 09 8C        |       | JNZ | L1       | ; repeat addition until ZF=1.    |

| 8C12H              | 23              |       | INX | Н        | ; Increment HL Reg pair          |

| 8C13H              | 77              |       | MOV | M,A      | ; store LSB of product           |

|                    |                 |       |     |          | in memory.                       |

| 8C14H              | 23              |       | INX | Н        | ; Increment HL Reg pair          |

| 8C15H              | 71              |       | MOV | M,C      | ; store MSB of product in        |

|                    |                 |       |     |          | memory.                          |

| 8C16H76            |                 | HLT   |     | ; ha     | lt the program.                  |

| <b>OUTPUT:</b>     |                 |       |     |          |                                  |

| 8C40::02           |                 |       |     |          |                                  |

| 8C41::03           |                 |       |     |          |                                  |

| 8C42::06           |                 |       |     |          |                                  |

| 8C43::00           |                 |       |     |          |                                  |

|                    |                 |       |     |          |                                  |

#### EXPERIMENT: 10 DIVISION OF TWO 8-BIT NUMBERS

#### **PROBLEM:**

Write an assembly language program to divide two numbers of 8 –bit data.

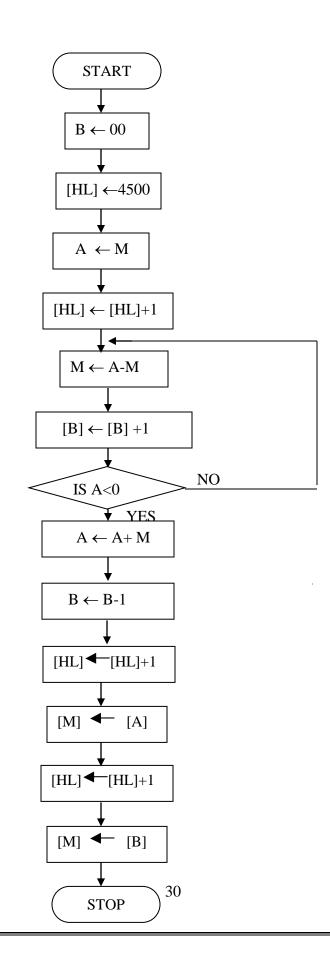

#### **ALGORITHM:**

- 1. Load Divisor and Dividend

- 2. Subtract divisor from dividend

- 3. Count the number of times of subtraction which equals the quotient

- 4. Stop subtraction when the dividend is less than the divisor .The dividend now becomes the remainder. Otherwise go to step 2.

- 5. Stop the program execution.

#### **FLOWCHART:**

#### ASSEMBLY LANGUAGE PROGRAM:

| ADDRESS | OPCODE | LABEL | MNEM<br>ONICS | OPERA<br>ND | COMMENTS                                       |

|---------|--------|-------|---------------|-------------|------------------------------------------------|

| 4100    | 06     |       | MVI           | B,00        | Clear B reg for quotient                       |

| 4101    | 00     |       |               |             |                                                |

| 4102    | 21     |       | LXI           | H,4500      | Initialize HL reg. to                          |

| 4103    | 00     |       |               |             | 4500H                                          |

| 4104    | 45     |       |               |             |                                                |

| 4105    | 7E     |       | MOV           | A,M         | Transfer dividend to acc.                      |

| 4106    | 23     |       | INX           | Н           | Increment HL reg. to point next mem. Location. |

| 4107    | 96     | LOOP  | SUB           | Μ           | Subtract divisor from dividend                 |

| 4108    | 04     |       | INR           | В           | Increment B reg                                |

| 4109    | D2     |       | JNC           | LOOP        | Jump to LOOP if result does                    |

| 410A    | 07     |       |               |             | not yield borrow                               |

| 410B    | 41     |       |               |             |                                                |

| 410C    | 86     |       | ADD           | Μ           | Add divisor to acc.                            |

| 410D    | 05     |       | DCR           | В           | Decrement B reg                                |

| 410E    | 23     |       | INX           | Н           | Increment HL reg. to point next mem. Location. |

| 410F    | 77     |       | MOV           | M,A         | Transfer the remainder from acc. to memory.    |

| 4110    | 23     |       | INX           | Н           | Increment HL reg. to point next mem. Location. |

| 4111    | 70     |       | MOV           | M,B         | Transfer the quotient from B reg. to memory.   |

| 4112    | 76     |       | HLT           |             | Stop the program                               |

#### **OUTPUT:**

4500::06

4501::03

4502::00

4503::02

#### EXPERIMENT: 11 16-BIT ADDITION

#### **PROGRAM:**

Write an assembly language program to add two numbers of 16-bit data stored in memory 8C40H, 8C41H and 8C42H, 8C43H. The data are stored such that LSB first and then MSB and store the result from 8C44H to 8C46H

#### **PROBLEM ANALYSIS:**

The 16-bit addition can be performed in 8085 microprocessor either in terms of 8-bit addition or by using DAD instruction. In addition using DAD instruction, one of the data should be in H L pair and another data can be another register pair. After addition the sum will be in H L register pair. If there is a carry in addition then that is indicated by setting carry flag. Hence one the register is used to account for carry.

#### **ALGORITHM:**

- 1 load the first data in H L register pair.

- 2. Move the first data to D E register pair.

- 3. Load the second data in H L register pair.

- 4. Clear A register for carry.

- 5. Add the content of D E pair to H L pair.

- 6. Check for carry. If carry =1, go to step 7 or if carry=0 go to step 8.

- 7. Increment carry register (A) to account for carry.

- 8. Store the sum and carry in memory.

- 9. Stop.

#### **FLOWCHART:**

#### ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE LAB<br>CODE | EL MNEMONIC | COMMENT                            |

|--------------------|---------------------|-------------|------------------------------------|

| 8C00H              | 2A 40 8C            | LHLD 8C40H  | ; get first data in HL reg. pair.  |

| 8C03H              | EB                  | XCHG        | ; store first data in DE reg. pair |

| 8C04H              | 2A 42 8C            | LHLD 8C42H  | ; get second data in HL reg. pair  |

| 8C07H              | AF                  | XRA A       | ; clear A register for carry       |

| 8C08H              | 19                  | DAD D       | ; get the sum in HL pair.          |

| 8C09H              | D2 0D 8C            | JNC L1      | ; if CY=0 go to L1                 |

| 8C0CH              | 3C                  | INR A       | ; if CY=1, increment A reg.        |

| 8C0DH              | 22 44 8C L1         | SHLD 8C44H  | ; store the sum in memory.         |

| 8C10H              | 32 46 8C            | STA 8C46H   | ; store the carry in memory.       |

| 8C13H              | 76                  | HLT         | ; halt the program                 |

#### **OUTPUT:**

8C40::02 8C41::03 8C42::05 8C43::00 8C44::07

8C45::03

8C46::00

#### EXPERIMENT: 12 <u>16-BIT SUBTRACTION</u>

#### PROGRAM:

Write an assembly language program to subtract two numbers of 16-bit data stored in memory from 8C40H to 8C43H. The data are stored such that LSB first and then MSB. Store the result in 8C44H and 8C45H.

#### **PROBLEM ANALYSIS:**

The 16-bit subtraction is performed in terms of 8-bit subtraction. First LSB's of the data are subtracted and the result is stored in memory. Then MSB's of the data are subtracted along with borrow in the previous subtraction and the result is stored in memory.

#### **ALGORITHM:**

- 1. Load the low byte of subtrahend in accumulator from memory and move is to B-register.

- 2. Load the low byte of minuend in accumulator from memory.

- 3. Subtract the content of B-register from the content of accumulator.

- 4. Store the low byte of result in memory.

- 5. Load the high byte of subtrahend in accumulator from memory and move it to B-register.

- 6. Load the high byte of minuend in accumulator from memory.

- 7. Subtract the content of B-register and the carry from the content of accumulator.

- 8. Store high byte of result in memory.

- 9. Stop the program.

#### **FLOWCHART:**

# ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE<br>CODE | MNEMONIC  | COMMENT                                                 |

|--------------------|-----------------|-----------|---------------------------------------------------------|

| 8C00H              | 3A 42 8C        | LDA 8C42H | ; get the LSB of subtrahend from 8C42H and store in Acc |

| 8C03H              | 47              | MOV B, A  | ; Move the LSB of subtrahend to B-register              |

| 8C04H              | 3A 40 8C        | LDA 8C40H | ; get the LSB of minuend in A-register                  |

| 8C07H              | 90              | SUB B     | ; get the difference of LSB's in A-register             |

| 8C08H              | 32 44 8C        | STA 8C44H | ; store the result in memory.                           |

| 8C0BH              | 3A 43 8C        | LDA 8C43H | ; get the MSB of subtrahend from 8C43H and store in Acc |

| 8C0EH              | 47              | MOV B, A  | ; Move the MSB of subtrahend to B-register.             |

| 8C0FH              | 3A 41 8C        | LDA 8C41H | ; get the MSB of minuend in A-register.                 |

| 8C12H98            |                 | SBB B     | ; get the difference of MSB's in A-register.            |

| 8C13H              | 32 45 8C        | STA 8C45H | ; store the result.                                     |

| 8C16H              | 76              | HLT       | ; halt the program                                      |

| <b>OUTPUT:</b>     |                 |           |                                                         |

| 8C40::05           |                 |           |                                                         |

| 8C41::03           |                 |           |                                                         |

| 8C42::02           |                 |           |                                                         |

| 8C43::01           |                 |           |                                                         |

| 8C44::03           |                 |           |                                                         |

| 8C45::02           |                 |           |                                                         |

| 8C46::00           |                 |           |                                                         |

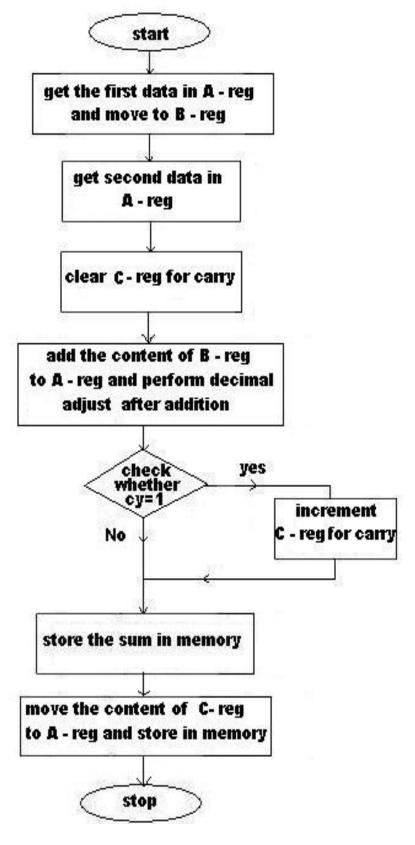

## EXPERIMENT: 13 TWO DIGIT BCD ADDITION

### **PROGRAM:**

Write an assembly language program to add two numbers of two digit (single precession) BCD data stored memory locations 8C40H and 8C41H. Store the result in 8C42H and 8C43H.

### **PROBLEM ANALYSIS:**

The 8085 microprocessor will perform only binary addition. Hence for BCD addition, the binary addition of BCD data is performed and then the sum is corrected to get result in BCD. After binary addition the following correction should be made to get the result in BCD.

- 1. if the sum of lower nibble exceeds 9 or if there is an auxiliary carry then 06 is added to lower nibble.

- 2. if the sum of upper nibble exceeds 9 or if there is carry then 06 is added to upper nibble.

The above correction is taken care by DAA instruction. Therefore after binary addition execute DAA instruction to do the above correction in the sum.

### **ALGORITHM:**

- 1. Load the first data in accumulator and move it to B-register.

- 2. Load the second data in accumulator.

- 3. Clear the C register for storing carry.

- 4. Add the content of B-register to accumulator.

- 5. Execute DAA instruction.

- 6. Check for carry. If carry=1, go to step 7 or if carry=0, go to step 8.

- 7. Increment C register to account for carry.

- 8. Store the sum in memory.

- 9. Move the carry (content of C register) to accumulator and store in memory.

10. Stop.

#### **FLOWCHART:**

40

# ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE LABE | L MNEMONIC | COMMENT                                        |

|--------------------|--------------|------------|------------------------------------------------|

| 8C00H              | 3A 40 8C     | LDA 8C40H  | ; get first data in accumulator.               |

| 8C03H              | 47           | MOV B, A   | ; transfer accumulator data to B-register.     |

| 8C04H              | 3A 41 8C     | LDA 8C41H  | ; get second data in A-register.               |

| 8C07H              | 0E 00        | MVI C, 00H | ; clear C register for accounting carry.       |

| 8C09H              | 80           | ADD B      | ; add the content of B-register to A-register. |

| 8C0AH              | 27           | DAA        | ; get the sum of BCD data in A- reg.           |

| 8C0BH              | D2 0E 8C     | JNC L1     | ; if CY=0, go to <b>L1.</b>                    |

| 8COEH              | 0C           | INR C      | ; if CY=1, increment C- reg.                   |

| 8C0FH              | 32 42 8C L1  | STA 8C42H  | ; store the sum in memory.                     |

| 8C12H              | 79           | MOV A, C   | ; move the carry to A- reg.                    |

| 8C13H              | 32 43 8C     | STA 8C43H  | ; store the carry in memory.                   |

| 8C16H76            | HLT          | ; halt     | t the program.                                 |

| OUTPUT:            |              |            |                                                |

| 8C40::80           |              |            |                                                |

| 8C41::80           |              |            |                                                |

| 8C42::60           |              |            |                                                |

| 8C43::01           |              |            |                                                |

41

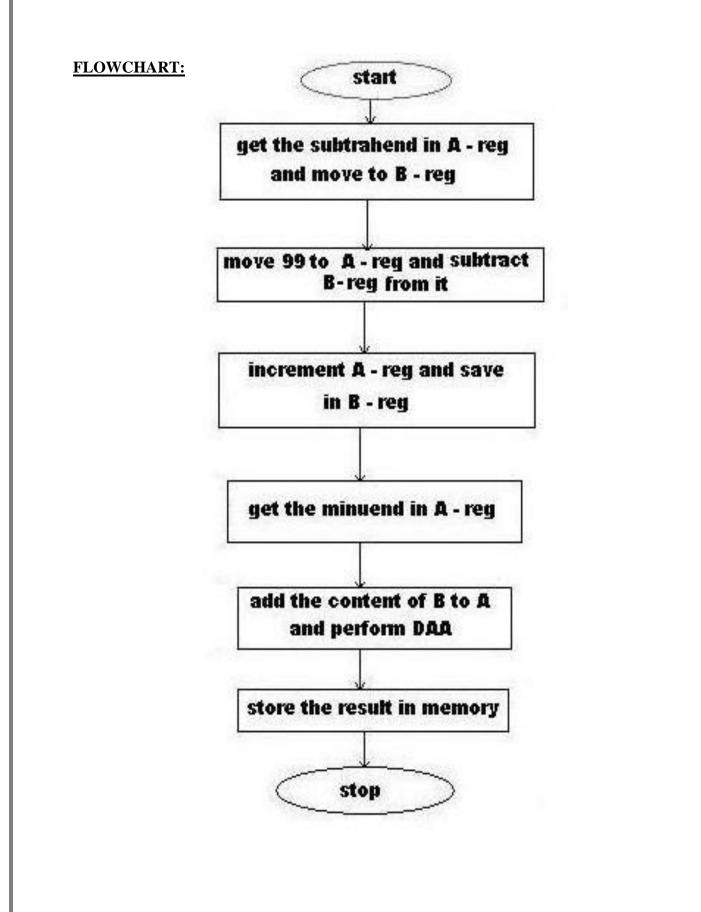

## EXPERIMENT 14 TWO DIGIT BCD SUBTRACTION

### PROGRAM:

Write an assembly language program to subtract BCD numbers of 2 digit BCD data stored in memory 8C40H and 8C41H. store the result in 8C42H.

### **PROBLEM ANALYSIS:**

The 8085 microprocessor will perform only binary subtraction. Hence for BCD subtraction 10's complement subtraction is performed. First the 10's complement of the subtrahend is obtained and then added to minuend. The DAA instruction is executed to get the result in BCD.

## **ALGORITHM:**

- 1. Load the subtrahend in A-register and move to B-register.

- 2. Move 99 to A-register and subtract the content of B-register from A-register.

- 3. Increment the A-register.

- 4. Move the content of A-register to B-register.

- 5. Load the minuend in A-register.

- 6. Add the content of B-register to a A-register.

- 7. Execute DAA instruction.

- 8. Store the result in memory.

- 9. Stop.

# ASSEMBLY LANGUAGE PROGRAM:

| MEMORY<br>LOCATION | MACHINE LAB | EL MNEMONIC | COMMENT                                                      |

|--------------------|-------------|-------------|--------------------------------------------------------------|

| 8COOH              | 3A 41 8C    | LDA 8C41H   | ; get the subtrahend in to accumulator.                      |

| 8CO3H              | 47          | MOV B,A     | ; move the data into B-register from A-reg.                  |

| 8CO4H              | 3E 99       | MVI A,99    | ; move the 99 to A-reg.                                      |

| 8C06H              | 90          | SUB B       | ; subtract the subtrahend from 99.                           |

| 8C07H              | 3C          | INR A       | ; 10's complement of subtrahend.                             |

| 8C08H              | 47          | MOV B,A     | ; store the 10's complement<br>of subtrahend in B            |

| 8CO9H              | 3A 40 8C    | LDA 8C40H   | ; get the minuend in A-register                              |

| 8COCH              | 80          | ADD B       | ; Get the BCD sum of minuend and 10'complemnt of subtrahend. |

| 8CODH              | 27          | DAA         | ; the sum is the difference between given BCD data.          |

| 8COEH              | 32 42 8C    | STA 8C42H   | ; store the result in memory.                                |

| 8C11H              | 76          | HLT         | ; halt the program.                                          |

| OUTPUT:            |             |             |                                                              |

| 8C40::80           |             |             |                                                              |

| 8C41::60           |             |             |                                                              |

| 8C42::20           |             |             |                                                              |

| 8C43::00           |             |             |                                                              |

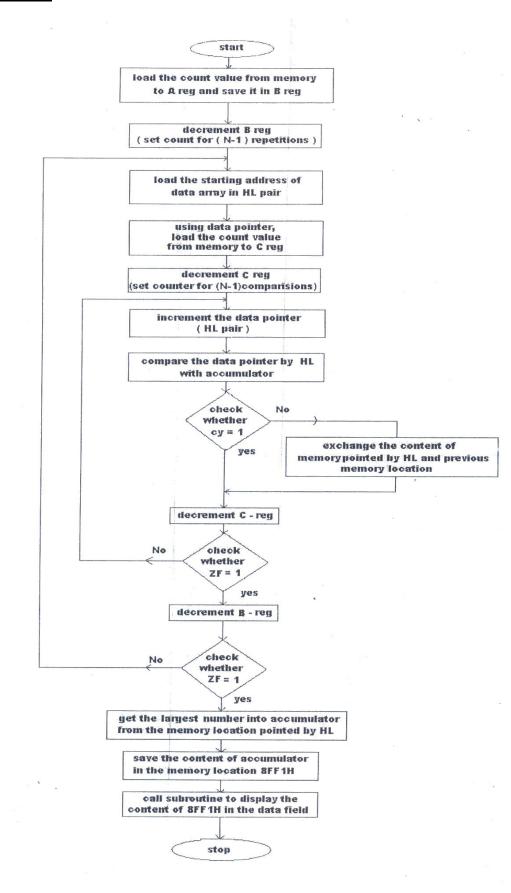

## EXPERIMENT 15 SORTING OF DATA IN ASCENDING ORDER AND FINDING LARGEST NUMBER IN THE ARRAY

### PROGRAM:

Write an assembly language program to sort an array of data in ascending order and find the largest number and display it in the data field. The array is stored in memory starting from 8C40H. The first element of the array gives the count value for the number of elements in the array.

### **PROBLEM ANALYSIS:**

The algorithm for bubble sorting is given below. In bubble sorting of N-data,

(N-1) comparisons are carried by taking two consecutive data at a time. After each comparison, the data are rearranged such that smallest among the two is in first memory location and largest in the next memory location. When we perform (N-1) comparisons as mentioned above, for (N-1) times then the array consisting of N-data will be sorted in the ascending order.

## **ALGORITHM:**

- 1. Load the count value from memory to A-reg. and save it in B-reg.

- 2. Decrement B-reg. (B is a count for N-1 repetitions)

- 3. Set H L pair as data address pointer.

- 4. Set C-register as counter for (N-1) comparisons.

- 5. Load a data of the array in accumulator using the data address pointer.

- 6. Increment the H L pair (data address pointer).

- 7. Compare the data pointed by H L with accumulator.

- 8. if carry flag is set (if the content of the accumulator is smaller than memory) then go to step 10, otherwise go to next step.

- 9. Exchange the content of memory pointed by H L and the accumulator.

- 10. Decrement C-register. if zero flag is reset go to the step 6 otherwise go to next step.

- 11. Decrement B-register. If zero flag is reset go to step 3 otherwise go to next step.

- 12. Load the largest value from memory into accumulator.

- 13. Store the content of accumulator in memory location 8FF1H.

- 14. Call subroutine to display the content of memory location 8FF1H into the data field.

15. Stop.

**FLOWCHART:**

# ASSEMBLY LANGUAGE PROGRAM:

| MEMOR        | RY M              | IACHI   | NE LABEL | MNEMONIC    | COMMENT                                                                                    |

|--------------|-------------------|---------|----------|-------------|--------------------------------------------------------------------------------------------|

| LOCAT        | ION (             | CODE    |          |             |                                                                                            |

| 8COOH        | 3A                | 40      | 8C       | LDA 8C4OH   | ; load the count value in A-reg.                                                           |

| 8CO3H        | 47                |         |          | MOV B,A     | ; set counter for (N-1)repetitions of                                                      |

| 8CO4H        | 05                |         |          | DCR B       | N-1 comparisons.                                                                           |

| 8CO5H        | 21                | 40      | 8C L2    | LXI H,8C4OH | ; set pointer for array.                                                                   |

| 8CO8H        | 4E                |         |          | MOV C,M     | ; set counter for (N-1) comparisons.                                                       |

| 8CO9H        | OD                |         |          | DCR C       | ;                                                                                          |

| 8COAH        | 23                |         |          | INX H       | ; increment pointer                                                                        |

| 8COBH        | 7E                |         | L1       | MOV A,M     | ; get one data of array in A-reg.                                                          |

| 8COCH        | 23                |         |          | INX H       | ; increment pointer.                                                                       |

| 8CODH        | BE                |         |          | CMP M       | ; compare next data with A-reg.                                                            |

| 8COEH        | DA                | 16      | 8C       | JC L3       | ; if content of A is less than<br>memory then go to <b>L3</b>                              |

| 8C11H        | 56                |         |          | MOV D,M     | ; if the content of A is greater than                                                      |

| 8C12H        | 77                |         |          | MOV M,A     | the content of memory then exchange                                                        |

| 8C13H        | 2B                |         |          | DCX H       | the content of memory pointed by H L                                                       |

| 8C14H        | 72                |         |          | MOV M,D     | and previous location.                                                                     |

| 8C15H        | 23                |         |          | INX H       | ;                                                                                          |

| 8C16H        | OD                |         | L3       | DCR C       | ; decrement C-register.                                                                    |

| 8C17H        | C2                | 0B      | 8C       | JNZ L1      | ; repeat comparisons until C reg. count is zero.                                           |

| 8C1AH        | 05                |         |          | DCR B       | ; decrement B-register.                                                                    |

| 8C1BH        | C2                | 05      | 8C       | JNZ L2      | ; repeat until B count is zero.                                                            |

| 8C1EH        | 7E                |         |          | MOV A,M     | ; get the largest number into accumulator.                                                 |

| 8C1FH        | 32                | F1      | 8F       | STA 8FF1H   | ; store the content of accumulator<br>in memory location 8FF1H.                            |

| 8C22H        | CD                | 4C      | 04       | CALL 044CH  | ; call subroutine to display the<br>content of the memory location<br>8FF1H in data field. |

| 8C25H<br>OUT | 76<br><b>PUT:</b> |         |          | HLT         | ; halt the program.                                                                        |

| 8C40         | ::03 8            | C43::03 |          |             |                                                                                            |

| 8C41         | ::01 8            | FF1::03 |          |             |                                                                                            |

| 8C42         | 02                |         |          |             |                                                                                            |

|              |                   |         |          |             |                                                                                            |

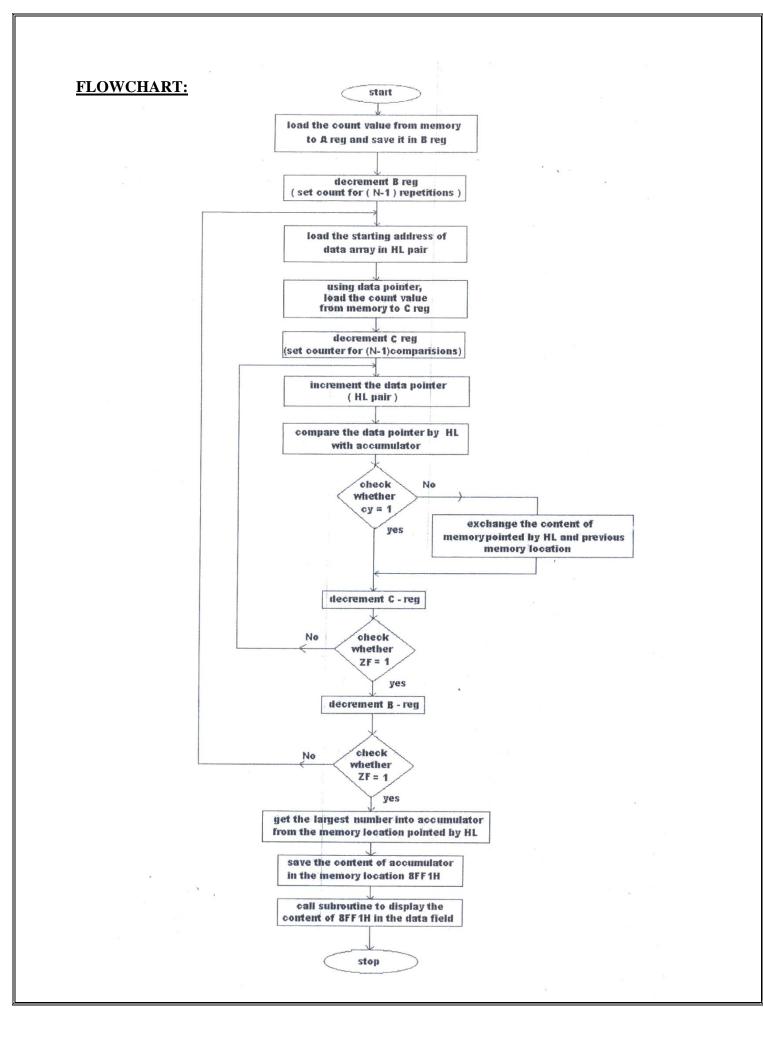

# EXPERIMENT 16 SORTING OF DATA IN DESCENDING ORDER AND FINDING SMALLEST NUMBER IN THE ARRAY

#### **PROGRAM:**

Write an assembly language program to sort an array of data in descending order and find the smallest number and display it in the data field. The array is stored in memory starting from 8C40H. The first element of the array gives the count value for the number of elements in the array.

#### **PROBLEM ANALYSIS:**

The algorithm for bubble sorting is given below. In bubble sorting of N-data, (N-1) comparisons are carried by taking two consecutive data at a time. After each comparison, the data are rearranged such that largest among the two is in first memory location and smallest in the next memory location. When we perform (N-1) comparisons as mentioned above, for N times then the array consisting of N-data will be sorted in the descending order.

#### **ALGORITHM:**

- 1. Load the count value from memory to A-reg. and save it in B-reg.

- 2. Decrement B-reg (B is a count for N-1 repetitions).

- 3. Set H L pair as data address pointer.

- 4. Set C-register as counter for (N-1) comparisons.

- 5. Load a data of the array in accumulator using the data address pointer.

- 6. Increment the H L pair (data address pointer).

- 7. Compare the data pointed by H L with accumulator.

- 8. If carry flag is reset (if the content of the accumulator is larger than memory) then go to step 10, otherwise go to next step.

- 9. Exchange the content of memory pointed by H L and the accumulator.

- 10. Decrement C-register. if zero flag is reset go to the step 6 otherwise go to next step.

- 11. Decrement B-register. If zero flag is reset go to step 3 otherwise go to next step.

- 12. Load the smallest value from memory into accumulator.

- 13. Store the content of accumulator in memory location 8FF1H.

- 14. Call subroutine to display the content of memory location 8FF1H into the

data field.

15. Stop.

| <u>ASSEMBLY</u><br>MEMORY<br>LOCATION | MAC | CHINE | LA | BEL | MNEM | ONIC    | COMMENT                                                                                                                                         |

|---------------------------------------|-----|-------|----|-----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 8COOH                                 | 3A  | 40    | 8C |     | LDA  | 8C4OH   | ; load the count value in A-reg.                                                                                                                |

| 8CO3H                                 | 47  |       |    |     | MOV  | B,A     | ; set counter for<br>(N-1) repetitions of                                                                                                       |

| 8CO4H                                 | 05  |       |    |     | DCR  | В       | N-1 comparisons.                                                                                                                                |

| 8CO5H                                 | 21  | 40    | 8C | L2  | LXI  | H,8C4OH | ; set pointer for array.                                                                                                                        |

| 8CO8H                                 | 4E  |       |    |     | MOV  |         | ; set counter for<br>(N-1) comparisons.                                                                                                         |

| 8CO9H                                 | OD  |       |    |     | DCR  | С       | ;                                                                                                                                               |

| 8COAH                                 | 23  |       |    |     | INX  | Н       | ; increment pointer                                                                                                                             |

| 8COBH                                 | 7E  |       |    | L1  | MOV  | A,M     | ; get one data of array in A-reg.                                                                                                               |

| 8COCH                                 | 23  |       |    |     | INX  | Н       | ; increment pointer.                                                                                                                            |

| 8CODH                                 | BE  |       |    |     | CMP  | М       | ; compare next data with A-reg.                                                                                                                 |

| 8COEH                                 | DA  | 16    | 8C |     | JNC  | L3      | ; if content of A is less than<br>memory then go to L3                                                                                          |

| 8C11H                                 | 56  |       |    |     | MOV  | D,M     | ; if the content of A is<br>greater than the content of<br>memory then exchange the<br>content of memory pointed<br>by H L and previous locatio |

| 8C12H                                 | 77  |       |    |     | MOV  | M. A    |                                                                                                                                                 |

| 8C13H                                 | 2B  |       |    |     |      | Н       |                                                                                                                                                 |

| 8C14H                                 | 72  |       |    |     | MOV  |         |                                                                                                                                                 |

| 8C15H                                 | 23  |       |    |     | INX  | H       |                                                                                                                                                 |

| 8C16H                                 | OD  |       |    | L3  | DCR  | C       | ; decrement C-register.                                                                                                                         |

| 8C17H                                 | C2  | 0B    | 8C |     |      | L1      | ; repeat comparisons until<br>C reg. count is zero.                                                                                             |

| 8C1AH                                 | 05  |       |    |     | DCR  | В       | ; decrement B -register.                                                                                                                        |

| 8C1BH                                 | C2  | 05    | 8C |     | JNZ  | L2      | ; repeat until B count is zero                                                                                                                  |

| 8C1EH                                 | 7E  |       |    |     | MOV  |         | ; get the smallest number into accumulator.                                                                                                     |

| 8C1FH                                 | 32  | F1    | 8F |     | STA  | 8FF1H   | ; store the content of<br>accumulator in memory<br>location 8FF1H.                                                                              |

| 8C22H                                 | CD  | 4C    | 04 |     | CALL | 044CH   | ; call subroutine to display th<br>content of the memory<br>location 8FF1H in data fiel                                                         |

| 8C25H                                 | 76  |       |    |     | HLT  |         | ; halt the program                                                                                                                              |

## EXPERIMENT 17 DIGITAL TO ANALOG CONVERSION

# a) To generate square wave at the DAC2 output

Source code:

|       |   | ORG 410 | 0             |

|-------|---|---------|---------------|

| START | : | MVI     | A, 00         |

|       |   | OUT     | <b>0C8H</b>   |

|       |   | CALL DE | LAY           |

|       |   | MVI     | A, OFF        |

|       |   | OUT     | <b>0C8H</b>   |

|       |   | CALL DE | LAY           |

|       |   | JMP     | START         |

| DELAY | : | MVI     | <b>B</b> , 05 |

| L1    | : | MVI     | C, 0FF        |

| L2    | : | DCR     | С             |

|       |   | JNZ     | L2            |

|       |   | DCR     | В             |

|       |   | JNZ     | L1            |

|       |   | RET     |               |

|       |   |         |               |

WAVEFORM:

## CALCULATION:

Amplitude:

Time Period:

**RESULT:** Hence the Square wave is generated.

b) To generate sine-wave at DAC1 output.

Source code:

|           |                                                                                                             | ORG                                                                                                                          | 4100H                                                |

|-----------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|           | :                                                                                                           | LXI                                                                                                                          | Н, 4110Н                                             |

|           |                                                                                                             | MVI                                                                                                                          | C, 46                                                |

| :         | MOV                                                                                                         | A, M                                                                                                                         | ,                                                    |

|           |                                                                                                             | OUT                                                                                                                          | <b>0C0H</b>                                          |

|           |                                                                                                             | INX                                                                                                                          | Η                                                    |

|           |                                                                                                             | DCR                                                                                                                          | С                                                    |

|           |                                                                                                             | JNZ                                                                                                                          | LOOP                                                 |

|           |                                                                                                             | JMP                                                                                                                          | START                                                |

| TABLE     | : (411                                                                                                      | 0)                                                                                                                           |                                                      |

| <b>8A</b> |                                                                                                             | 95                                                                                                                           | <b>A0</b>                                            |

| <b>B5</b> |                                                                                                             | BF                                                                                                                           | <b>C8</b>                                            |

| D9        |                                                                                                             | EO                                                                                                                           | <b>E7</b>                                            |

| F2        |                                                                                                             | F7                                                                                                                           | FA                                                   |

| FE        |                                                                                                             | FF                                                                                                                           | FE                                                   |

| FA        |                                                                                                             | F7                                                                                                                           | <b>F2</b>                                            |

| <b>E7</b> |                                                                                                             | EO                                                                                                                           | D9                                                   |

| <b>C8</b> |                                                                                                             | BF                                                                                                                           | <b>B5</b>                                            |

| <b>A0</b> |                                                                                                             | 95                                                                                                                           | <b>8A</b>                                            |

| 74        |                                                                                                             | 69                                                                                                                           | <b>5</b> F                                           |

| 49        |                                                                                                             | <b>3</b> F                                                                                                                   | 36                                                   |

| 25        |                                                                                                             | 1D                                                                                                                           | 17                                                   |

| <b>0B</b> |                                                                                                             | 07                                                                                                                           | 04                                                   |

| 00        |                                                                                                             | 01                                                                                                                           | 04                                                   |

| <b>0B</b> |                                                                                                             | 10                                                                                                                           | 17                                                   |

| 25        |                                                                                                             | <b>2D</b>                                                                                                                    | 36                                                   |

| 49        |                                                                                                             | 53                                                                                                                           | 57                                                   |

| 74        |                                                                                                             |                                                                                                                              |                                                      |

|           | TABLE<br>8A<br>B5<br>D9<br>F2<br>FE<br>FA<br>E7<br>C8<br>A0<br>74<br>49<br>25<br>0B<br>00<br>0B<br>25<br>49 | : MOV<br>TABLE : (4110<br>8A<br>B5<br>D9<br>F2<br>FE<br>FA<br>E7<br>C8<br>A0<br>74<br>49<br>25<br>0B<br>00<br>0B<br>25<br>49 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

WAVEFORM:

CALCULATION: Amplitude: **RESULT:** Hence the Sine wave is generated.

Time Period:

# c) To generate triangular waveform at DAC2 output

# Source code:

|       |   | ORG 4100 | )H      |

|-------|---|----------|---------|

| START | : | MVI      | L, 00   |

| L1    | : | MOV A, L | ı       |

|       |   | OUT      | 0C8H    |

|       |   | INR      | L       |

|       |   | JNZ      | L1      |

|       |   | MVI      | L, OFFH |

| L2    | : | MOV A, L | ı       |

|       |   | OUT      | 0C8H    |

|       |   | DCR      | L       |

|       |   | JNZ      | L2      |

|       |   | JMP      | START   |

## CALCULATION:

Amplitude:

Time Period:

**RESULT:** Hence the Triangular wave is generated.

# d) To create a saw-tooth wave at the output of DAC1.

Source code:

|       |   | ORG | <b>4100H</b> |

|-------|---|-----|--------------|

| START | : | MVI | А, 00Н       |

| L1    | : | OUT | <b>0C0H</b>  |

|       |   | INR | Α            |

|       |   | JNZ | L1           |

|       |   | JMP | START        |

CALCULATION: Amplitude:

Time Period:

**RESULT:** Hence the Saw-tooth wave is generated.

## EXPERIMENT 18 STEPPER MOTOR CONTROLLER

#### a. Stepper motor at different speeds

**Aim:** To write an ALP for run a stepper motor at different speeds in two directions and observe the actions which takes place.

## **Apparatus:**

- 1. Micro-85EB 8085 µP kit

- 2. Stepper motor Interface Module

- 3. Bus card

## Source Code:

| START:   | LXI | H, LO        | OOK UF   | )  |

|----------|-----|--------------|----------|----|

|          | MVI | <b>B</b> ,04 |          |    |

| REPT:    | MOV | A,M          |          |    |

|          | OUT | 0C0H         | [        |    |

|          | LXI | D, 03        | 03H      |    |

| DELAY    | NOP |              |          |    |

|          | DCX | D            |          |    |

|          | MOV | A,E          |          |    |

|          | ORA | D            |          |    |

|          | JNZ | DEL          | AΥ       |    |

|          | INX | Η            |          |    |

|          | DCR | В            |          |    |

|          | JNZ | REPT         | <b>[</b> |    |

|          | JMP | STAI         | RΤ       |    |

| LOOK UP: |     |              |          |    |

| DB:      | 09  | 05           | 06       | 0A |

#### **Procedure:**

- 1. Enter the above program starting from 4100h. Connect the stepper motor in port1 and execute.

- 2. The stepper motor can be rotates. Speed can be varied by varying the count at DE pair.

- 3. Direction can be varied by entering the data in the LOOK UP table in the reverse order.

## **b.** Stepper motor at different angles

**Aim:** To write an ALP for run a stepper motor for required angle within 360<sup>0</sup>, which is equivalent to 256 steps.

## **Apparatus:**

- 1. Micro-85EB 8085 µP kit

- 2. Stepper motor Interface Module

- 3. Bus card

### Source Code:

|          | MVI    | C, HEX DATA |

|----------|--------|-------------|

| STAR1    | Γ: LXI | H, LOOK UP  |

|          | MVI    | B,04        |

| REPT:    | MOV    | A,M         |

|          | OUT    | C0          |

|          | DCR    | С           |

|          | JZ     | END         |

|          | LXI    | D, COUNT    |

| DELAY    | Y: NOP |             |

|          | DCX    | D           |

|          | MOV    | A,E         |

|          | ORA    | D           |

|          | JNZ    | DELAY       |

|          | INX    | Н           |

|          | DCR    | В           |

|          | JNZ    | REPT        |

|          | JMP    | START       |

| LOOK UP: |        |             |

| DB       | :09 05 | 06 0A       |

| END:     | HLT    |             |

## **Procedure:**